# INTEL® XEON® PROCESSOR D-1500 PRODUCT FAMILY THERMAL/MECHANICAL SPECIFICATION AND DESIGN GUIDE

Intel Corporation November 2015

Reference Number: 332055-002

### Legal Disclaimer

Notice: This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at Intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting <a href="https://www.intel.com/design/literature.htm">www.intel.com/design/literature.htm</a>.

Intel, Xeon, and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2015, Intel Corporation. All Rights Reserved.

### **Revision History**

| Revision | Comments                                                                                                                                                                                                  | Date          |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 002      | <ul> <li>Added 6-core Microserver SKU.</li> <li>Added Networking, IOTG, and Storage<br/>SKUs.</li> <li>Added reference heatsink information<br/>for Networking, IOTG, and Storage<br/>segments</li> </ul> | November 2015 |

### **Contents**

- <u>Introduction</u>

- References

- Definition of Terms

- Package Information

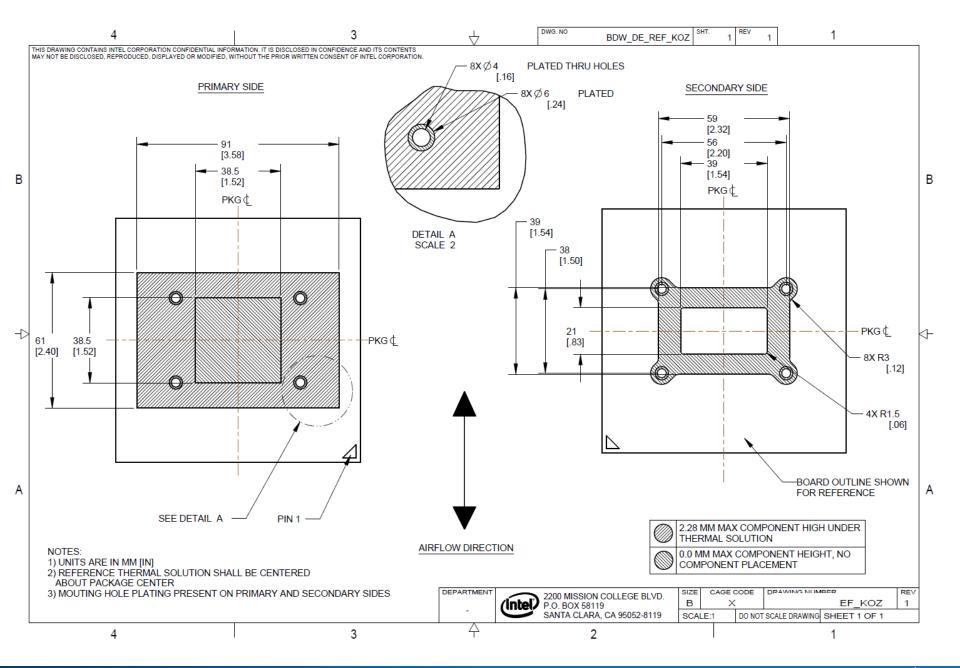

- Package mechanical drawing

- Solder ball land pattern requirements

- Thermal Information

- Thermal, Power and SKU Summary

- Thermal Features

- Reference Designs and Suppliers for each segment

- Microserver reference thermal solutions

- Storage reference thermal solutions

- Communications Infrastructure reference thermal solutions

- Appendix A Intel® Xeon® Processor D-1500 Product Family Package Mechanical Drawing

- Appendix B Standard Heatsink Mechanical Drawings

- Appendix C Low Profile Heatsink Mechanical Drawings

- Appendix D SBB Standard Storage Heatsink Mechanical Drawings

- Appendix E ATCA\* Reference Heatsink Mechanical Drawings

- Appendix F CPCI\* Reference Heatsink Mechanical Drawings

- Appendix G Heatsink Suppliers

### Introduction

This document provides specifications and guidelines for the design of thermal and mechanical solutions for Intel® Xeon® Processor D-1500 Product Family for Microserver, Storage, and Communications segments.

The specifications and design guidelines apply to Intel<sup>®</sup> Xeon<sup>®</sup> Processor D-1500 Product Family in their current stage of development and *are subject to change*.

The reference thermal solutions described in this document include:

- Heatsink

- Retention hardware

The goal of this document is to enable board and system thermal mechanical designers and suppliers of SoC heatsinks to design thermal solutions for Intel® Xeon® Processor D-1500 Product Family.

The Intel® Xeon® Processor D-1500 Product Family SKU summary is located <u>here</u>.

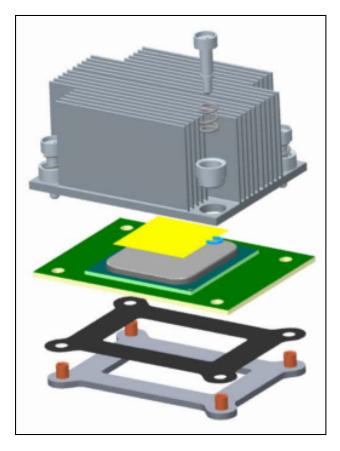

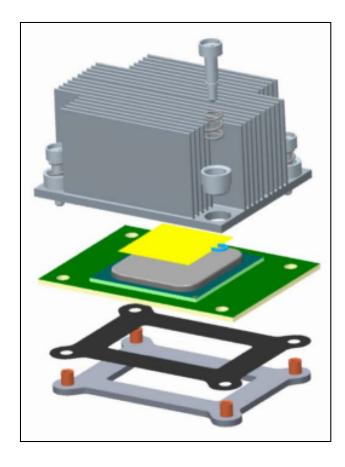

Nominal reference heatsink for Microserver

### References

| Document                                                                                                                            | Reference                                       | Notes         |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------|

| Intel® Xeon® Processor D-1500 Product Family Datasheet - Volume 1 of 4: Integrated Platform Controller Hub                          | 332050                                          | 1             |

| Intel® Xeon® Processor D-1500 Product Family Datasheet - Volume 2 of 4: Registers                                                   | 332051                                          | 1             |

| Intel® Xeon® Processor D-1500 Product Family Datasheet - Volume 3 of 4: Electrical                                                  | 332052                                          | 1             |

| Intel® Xeon® Processor D-1500 Product Family Datasheet - Volume 4 of 4: Intel® Xeon® Processor D-1500 Product Family LAN Controller | 332053                                          | 1             |

| Storage Bridge Bay Specification                                                                                                    | http://sbbwg.org                                |               |

| Running Average Power Limit (RAPL) White Paper                                                                                      | 495964                                          | www.intel.com |

| System Mechanical Design Guidance for Dynamic Events - Application Notes /Briefs                                                    | 383578                                          |               |

| Board Flexure Initiative (BFI) - Manufacturing Advantage Service (MAS)                                                              | http://www.intel.com/<br>design/quality/cme.htm |               |

| Server Systems Infrastructure (SSI) - Microserver Micromodule Specification                                                         | http://ssiforum.org                             |               |

| PICMG Specifications (AdvancedTCA, AdvancedMC, etc.)                                                                                | http://www.picmg.org                            |               |

| Form Factor Specifications (Motherboard, Power Supply, Riser, etc.)                                                                 | http://www.formfactors.org                      |               |

| 1. Contact your Field Sales Representative for the latest version of this document.                                                 |                                                 |               |

### **Definition of Terms**

| Term                  | Description                                                                                                                                                                                                                             |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATCA                  | Advanced Telecommunications Computing Architecture                                                                                                                                                                                      |

| Bypass                | Bypass is the area between a passive heatsink and any object that can act to form a duct. For this example, it can be expressed as a dimension away from the outside dimension of the fins to the nearest surface.                      |

| CPCI                  | Compact Peripheral Component Interconnect                                                                                                                                                                                               |

| DTS                   | Digital Thermal Sensor                                                                                                                                                                                                                  |

| FSC                   | Fan Speed Control                                                                                                                                                                                                                       |

| IHS                   | Integrated Heat Spreader                                                                                                                                                                                                                |

| IOTG                  | Internet of Things Group                                                                                                                                                                                                                |

| PECI                  | The Platform Environment Control Interface (PECI) is a one-wire interface that provides a communication channel between SoC and chipset components to external monitoring devices                                                       |

| $\Psi_{ca}$           | Case-to-ambient thermal characterization parameter (psi). A measure of thermal solution performance using Total Package Power. Defined as (T <sub>CASE</sub> – TLA) / (TDP). Heat source should always be specified for Y measurements. |

| $\Psi_{\sf cs}$       | Case-to-sink thermal characterization parameter. A measure of thermal interface material performance using Total Package Power. Defined as $(T_{CASE} - T_{SINK})$ / (TDP).                                                             |

| SoC                   | System On a Chip.                                                                                                                                                                                                                       |

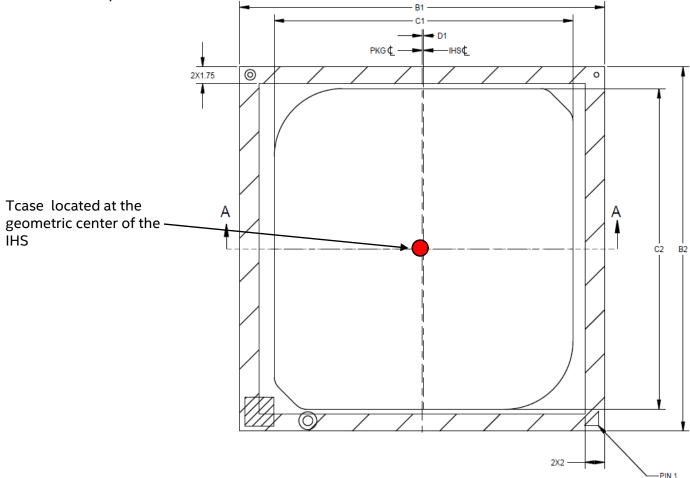

| T <sub>CASE</sub>     | The case temperature of the SoC measured at the geometric center of the topside of the IHS.                                                                                                                                             |

| T <sub>CASE-MAX</sub> | The maximum case temperature as specified in a component specification.                                                                                                                                                                 |

### **Definition of Terms Continued**

| Term            | Description                                                                                                                                                                                                                                         |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| тсс             | Thermal Control Circuit: thermal monitor uses the TCC to reduce the die temperature by using clock modulation and /or operating frequency and input voltage adjustment when the die temperature is very near its operating limits.                  |

| TDP             | Thermal Design Power: thermal solution should be designed to dissipate this target SOC power level. TDP is not the maximum power that the SoC can dissipate.                                                                                        |

| Thermal Monitor | A power reduction feature designed to decrease temperature after the SoC has reached its maximum operating temperature.                                                                                                                             |

| TIM             | Thermal Interface Material: The thermally conductive compound between the heatsink and the SoC integrated heat spreader (IHS). This material fills the air gaps and voids, and enhances the transfer of the heat from the SoC case to the heatsink. |

| T <sub>LA</sub> | The measured ambient temperature locally surrounding the SoC. The ambient temperature should be measured just upstream of a passive heatsink or at the fan inlet for an active heatsink.                                                            |

| T <sub>SA</sub> | The system ambient air temperature external to a system chassis. This temperature is usually measured at the chassis air inlets.                                                                                                                    |

| TTV             | Thermal Test Vehicle                                                                                                                                                                                                                                |

| KOZ             | Keep Out Zone                                                                                                                                                                                                                                       |

| SJR             | Solder Joint Reliability                                                                                                                                                                                                                            |

| SRO             | Solder Resist Opening                                                                                                                                                                                                                               |

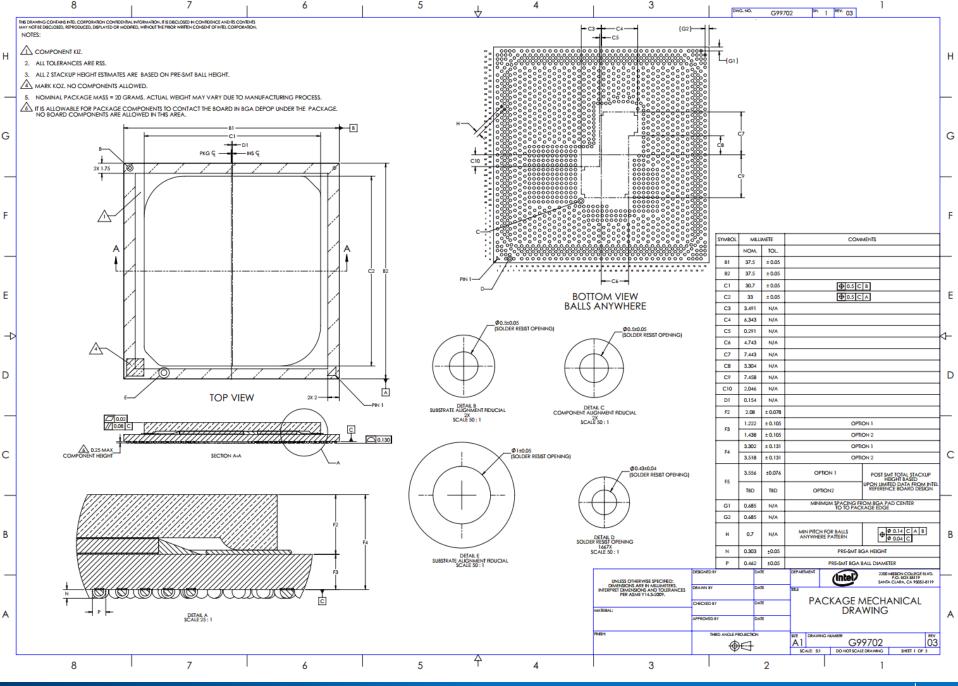

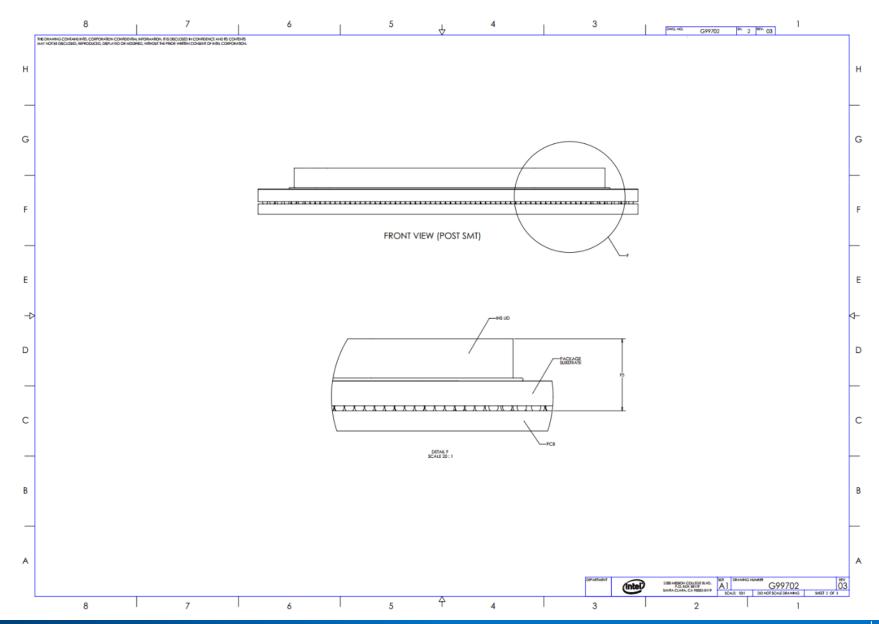

### PACKAGE INFORMATION

Intel® Xeon® Processor D-1500 Product Family

Package

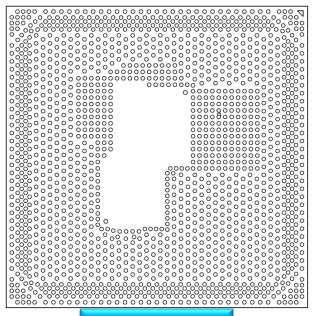

| Attribute                                    | Intel® Xeon® Processor D-<br>1500 Product Family |

|----------------------------------------------|--------------------------------------------------|

| Package                                      | 1667 Ball FCBGA                                  |

| Solder Ball Diameter <sup>1</sup>            | 0.462 mm                                         |

| Solder Ball Pitch                            | 0.7 mm, Variable                                 |

| Substrate Size <sup>1</sup>                  | 37.5 mm x 37.5 mm                                |

| Substrate Thickness <sup>1</sup>             | 1.222 mm                                         |

| Integrated Heat Spreader Height <sup>1</sup> | 2.08 mm                                          |

| Package Height <sup>1,2</sup>                | 3.556 mm                                         |

| Min/ Max Static Loading – with backplate     | 0 Lbf min, 35 Lbf max                            |

| Min/ Max Static Loading – without backplate  | 0 Lbf min, 15 Lbf max                            |

| Non-Critical to Function solder balls        | 114                                              |

#### Notes:

- 1. All dimensions are nominal

- 2. Package height is from the top of Integrated Heat Spreader (IHS) to bottom of the solder balls, Pre-SMT

**BALL PATTERN**

### Intel® Xeon® Processor D-1500 Product Family

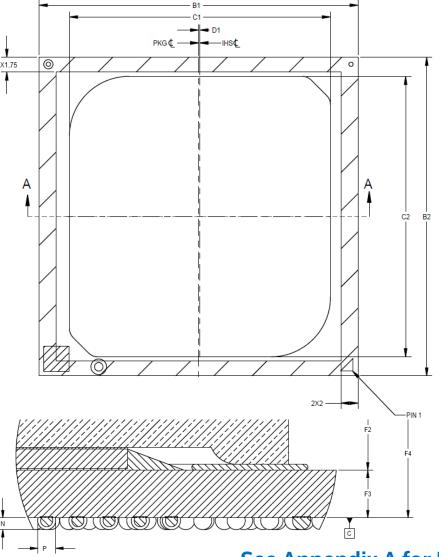

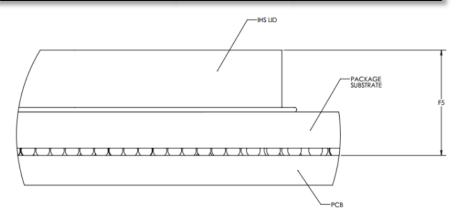

**Mechanical Drawing**

| Symbol | Nominal<br>(mm) | Tolerance<br>(mm) |

|--------|-----------------|-------------------|

| B1     | 37.5            | ± 0.05            |

| B2     | 37.5            | ± 0.05            |

| C1     | 30.7            | ± 0.05            |

| C2     | 33              | ± 0.05            |

| D1     | 0.154           | N/A               |

| F2     | 2.08            | ± 0.078           |

| F5     | 3.556           | ± 0.076           |

**See Appendix A for Detailed Mechanical Drawing**

### THERMAL INFORMATION

### **SoC Thermal Specifications**

The SoC requires a thermal solution to maintain temperatures within operating limits. Any attempt to operate the SoC outside these limits may result in permanent damage to the SoC and potentially other components within the system. Maintaining the proper thermal environment is key to reliable, long-term system operation.

A complete solution includes both component and system level thermal management features. Component level thermal solutions can include active or passive heatsinks in contact with the SoC integrated heat spreader (IHS). Typical system level thermal solutions may consist of system fans combined with ducting and venting.

To allow optimal operation and long-term reliability of Intel SoC-based systems, the SoC must remain within the case temperature ( $T_{CASE}$ ) specifications as defined in <u>here</u>.

### Intel® Xeon® Processor D-1500 Product Family Thermal, Power and SKU Summary – <u>Microserver</u>

| Core<br>Count | TDP<br>(W) | Non-Uniform Power Correction Factor <sup>1</sup> (C/W) | T <sub>CASE_MAX</sub><br>(°C) | T <sub>CASE_MIN</sub><br>(°C) | DTSmax<br>(°C) | Tcontrol<br>(°C) | Notes       |

|---------------|------------|--------------------------------------------------------|-------------------------------|-------------------------------|----------------|------------------|-------------|

| 8             | 45         | 0.05                                                   | 80                            | 0                             | 96             | 10               | 1,2,3,4,5,6 |

| 6             | 45         | 0.05                                                   | 80                            | 0                             | 99             | 10               | 1,2,3,4,5,6 |

| 4             | 45         | 0.04                                                   | 80                            | 0                             | 102            | 10               | 1,2,3,4,5,6 |

#### **Notes**

- 1. CF is the non-uniform heating correction factor in °C/W is defined as: CF=  $\Psi_{CA\_SoC}$   $\Psi_{CA\_uniform\_heating\_TTV\_model}$ . It should be used to adjust  $\Psi_{CA}$  calculations or measurements based on the TTV thermal model/hardware that Intel provides to account for power density effect of operational silicon.

- 2. T<sub>CASE</sub> is measured at the geometric center at the top surface of the Integrated Heat Spreader

- 3. Thermal Design Power (TDP) should be used as a target for SoC thermal solution design at maximum  $T_{CASE}$ . SoC power may exceed TDP for short durations. Please see Intel® Turbo Boost Technology for details.

- 4. These specifications are based on initial pre-silicon simulations, which will be updated as further characterization data becomes available.

- 5. Power specifications are defined at all VIDs found in the Intel® Xeon® Processor D-1500 Product Family SoC Datasheet. SoCs may have multiple VIDs for each frequency.

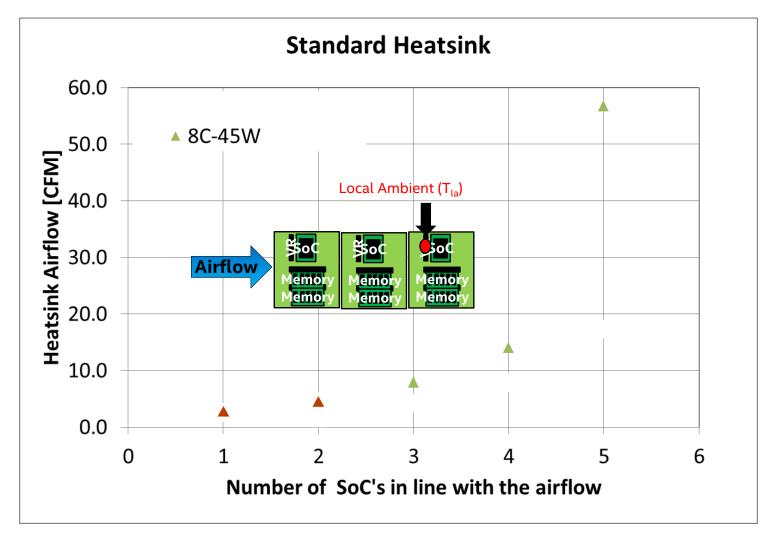

- 6. Based on <u>3 nodes in-line of the airflow</u> and using the <u>Standard reference heatsink</u>.

### Intel® Xeon® Processor D-1500 Product Family Thermal, Power and SKU Summary – Networking, IOTG, and Storage

| Core Count | TDP (W) | Non-Uniform<br>Power<br>Correction<br>Factor <sup>1</sup><br>(C/W) | T <sub>CASE_MAX</sub><br>(°C) | T <sub>CASE</sub> | EMIN | DTSmax<br>(°C) | Tcontrol<br>(°C) | Notes         |

|------------|---------|--------------------------------------------------------------------|-------------------------------|-------------------|------|----------------|------------------|---------------|

| 8          | 45      | 0.05                                                               | 89                            | 0                 |      | 104            | 22               | 1,2,3,4,5     |

| 8          | 35      | 0.05                                                               | 92                            | -40               | 0    | 104            | 22               | 1,2,3,4,5,6,7 |

| 6          | 35      | 0.06                                                               | 88                            | 0                 |      | 104            | 22               | 1,2,3,4,5     |

| 4          | 35      | 0.06                                                               | 85                            | 0                 |      | 104            | 22               | 1,2,3,4,5     |

| 4          | 25      | 0.05                                                               | 93                            | -40               | 0    | 104            | 22               | 1,2,3,4,5,6,7 |

| 2          | 25      | 0.04                                                               | 92                            | 0                 |      | 104            | 22               | 1,2,3,4,5     |

| 2          | 20      | 0.04                                                               | 96                            | 0                 |      | 106            | 22               | 1,2,3,4,5     |

#### Notes

- 1. CF is the non-uniform heating correction factor in  ${}^{\circ}$ C/W is defined as: CF=  $Y_{CA\_SoC}$   $Y_{CA\_uniform\_heating\_TTV\_model}$ . It should be used to adjust  $Y_{CA}$  calculations or measurements based on the TTV thermal model/hardware that Intel provides to account for power density effect of operational silicon.

- 2. T<sub>CASE</sub> is measured at the geometric center at the top surface of the Integrated Heat Spreader

- 3. Thermal Design Power (TDP) should be used as a target for SoC thermal solution design at maximum  $T_{CASE}$ . SoC power may exceed TDP for short durations. Please see Intel® Turbo Boost Technology for details.

- 4. These specifications are based on initial pre-silicon simulations, which will be updated as further characterization data becomes available.

- 5. Power specifications are defined at all VIDs found in the Intel® Xeon® Processor D-1500 Product Family SoC Datasheet. SoCs may have multiple VIDs for each frequency.

- 6. SKU configuration available as an eTEMP (Extended Temperature) or a Standard Temperature Part.

- 7. SKUs are only validated up to 90°C of dynamic range, Intel does not guarantee that the sku will operate properly outside this range. Dynamic range = absolute (Operating temp Boot Temperature).

### What is eTemp?

#### **Definition**

• Extended temperature or eTEMP is a stringent operating temperature range that ensures that a electrical or mechanical component will operate reliably in a -40°C to 85°C environment.

#### What does the Operating Temperature Mean?

- Cold: The lowest local system boot temperature of the device (Cold Soak).

- $T_{AIR} = T_{LA} = T_{Case-MIN}$

- Hot: The hottest local temperature ~1" (25mm)† upstream of the component.

- T<sub>AIR</sub> < T<sub>LA</sub> < T<sub>Case-MAX</sub>

#### Does this mean that $T_{Case-MAX}$ will change for eTEMP?

• No. T<sub>Case-MAX</sub> is a component level specification and should not be confused with eTEMP operating temperature ranges.

### What about T<sub>Case-MIN</sub>?

•  $T_{Case-MIN}$  will change to meet -40°C.  $T_{Case-MIN}$  will be equal to the operating ambient temperature during cold soak durations.  $T_{Case}$  does not need to be maintained at -40°C after boot.

(†This distance may need to be reduced depending on system density and upstream components.)

### **Tcontrol Overview**

Customers are required to maintain the SoC temperature, as measured by the DTS, at or below the Tcontrol temperature to ensure long term reliability of the SoC. The Tcontrol specification is an offset from DTSmax, resulting in the following equation for calculating the Tcontrol temperature:

Tcontrol temperature = DTSmax – Tcontrol

The SoC temperature can be calculated by the following equation:

DTS temperature = DTSmax – DTS offset

The following actions summarize required responses to the Tcontrol temperature:

- DTS Temperature < Tcontrol temperature → The system can run under any desired fan speed control condition.

- DTS Temperature = Tcontrol temperature → Tcontrol limit attained, system must increase fan speed to reduce DTS temperature below Tcontrol temperature.

- DTS Temperature > Tcontrol temperature → Fan speed increase is required to maintain Tcase below Tcase-max.

Note: SoC temperature (either Tcase or DTS) may exceed Tcontrol for a duration totalling less than 360 hours per year without affecting long term reliability (life) of the SoC.

### Thermal Management Features

The following is a list of supported features on the SoC:

- **Digital Thermal Sensor** On-die sensor for SoC temperature monitoring.

- Intel® Adaptive Thermal Monitor- The Adaptive Thermal Monitor feature provides an enhanced method for controlling the SoC temperature when the SoC silicon exceeds the Thermal Control Circuit (TCC) activation temperature

- **THERMTRIP** in the event of cathastrophic cooling failure the SoC will automatically shut down when the silicon has reached and elevated temperature. THERMTRIP N, a non-user configurable and non-software visible signal, will go active and stay active

- **PROCHOT N support** The PROCHOT N signal is bi-directional in that it can either signal when the SoC (any core) has reached its maximum operating temperature or be driven from an external source to activate the TCC.

- On-Demand Mode The SoC provides an auxiliary mechanism that allows system software to force the SoC to reduce its power consumption.

- **Memory Thermal Throttling** The purpose is to protect DIMMs from excess temperature which can cause harm over time, as well as ensure that the proper refresh rate is achieved. Closed Loop Thermal Throttling, Open Loop Thermal Throttling and DDR01 MEMHOT N Signal are features available

- Running Average Power Limit (RAPL) This feature allows setting a power budget on the SoC domain (a.k.a. core or package RAPL) that limits total SoC power through frequency reduction. It also allows monitoring of performance (frequency) and average SoC power for a user configurable time window ("running average" approach). This feature provides a variety of potential benefits, including meeting power budgets and maintaining thermal/power limits at the system, rack and/or data center levels.

- Platform Environment Control Interface (PECI) An Intel-defined, one-wire bus interface that provides a communication channel between Intel processors and external system management devices. The interface enables an external management controller to obtain thermal data from sensors integrated into components in the system. For details on PECI implementation and commands, refer to the Platform Environment Control Interface (PECI) Specification.

Please consult the Datasheet for details.

### Tcase Metrology

The following supplier can machine the groove and attach a thermocouple to the IHS. The supplier is listed below as a convenience to Intel's general customers and the list may be subject to change without notice. THERM-X OF CALIFORNIA Inc, 3200 Investment Blvd., Hayward, Ca 94545.

George Landis +1-510-441-7566 Ext. 368 georgel@therm-x.com

The vendor part number is XTMS1565.

Consult Intel® Xeon® Processor D-1500 Product Family SoC Thermal Test Vehicle User's Guide

listed in the references for further instrumentation details

## REFERENCE DESIGNS AND SUPPLIERS FOR EACH SEGMENT

### MICROSERVER REFERENCE DESIGN

### Reference Thermal Solution Assumptions - Standard Heatsink

| Power<br>SKU | Number of nodes in-line with the direction of the airflow                                                                                                                                                     | Key Assumptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45W          | Local Ambient (T <sub>la</sub> )  Airflow  Soc  Hemory  Memory  Memory  Local Ambient (T <sub>la</sub> )  Airflow  Local Ambient (T <sub>la</sub> )  Memory  Memory  Memory  Local Ambient (T <sub>la</sub> ) | The enabling boundary conditions are based on the following assumptions:  ASHRAE class A2 environment.  Micro-module channel airflow: 30CFM.  Local ambient temperature at the last node assumes 85% TDP for upstream nodes.  Pitch between micromodules: 42mm.  Airflow management to maximize heatsink flow. Notes:  Customer node density may vary.  Node density changes may drive SoC temperature specification changes.  Module width may vary depending on customer implementation, in this case a width between ~254 mm and ~305 mm and a height of ~119 mm was considered.  Micromodule channel  Standard Reference heatsink  SODIMM  Pitch |

### Heatsink Airflow Guidance\* as a function of Nodes In-line (cont'd)

<sup>\*</sup> Using conditions <u>above</u>. Customer implementations may vary

### System Reference Boundary Conditions

| SoC Power<br>Range SKU | Reference<br>Heatsink<br>Concept | Local ambient<br>Temperature, T <sub>la</sub><br>(°C) | Airflow<br>through<br>Heatsink<br>(CFM) | Notes |

|------------------------|----------------------------------|-------------------------------------------------------|-----------------------------------------|-------|

| 45W                    | Standard                         | 48.7                                                  | 7.9                                     | 1     |

#### Notes:

<sup>1. 3</sup> nodes in-line with the direction of the airflow

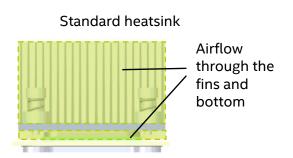

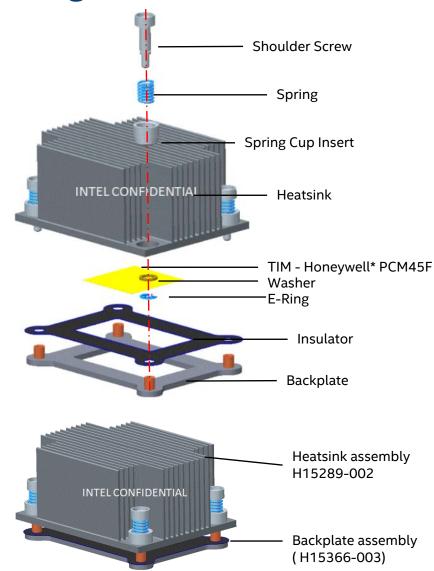

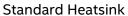

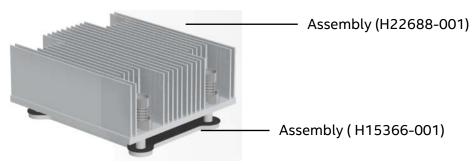

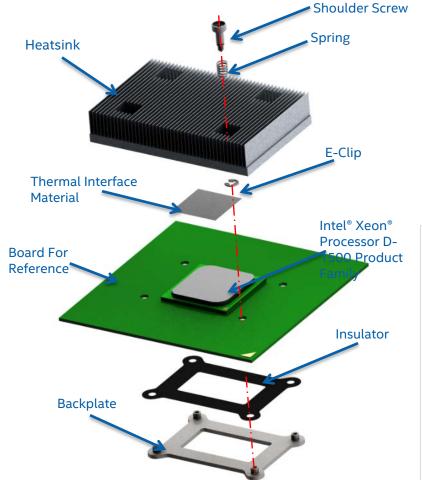

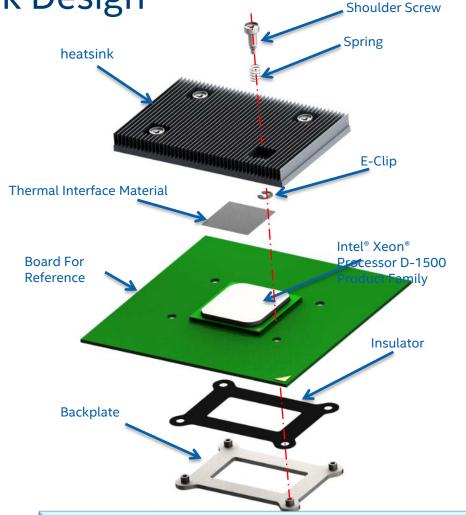

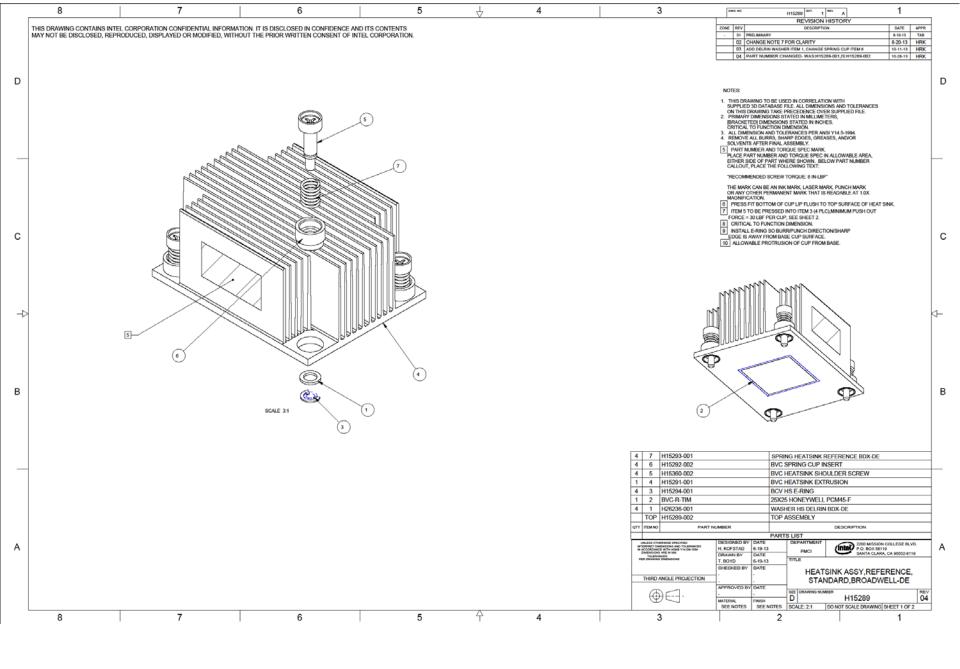

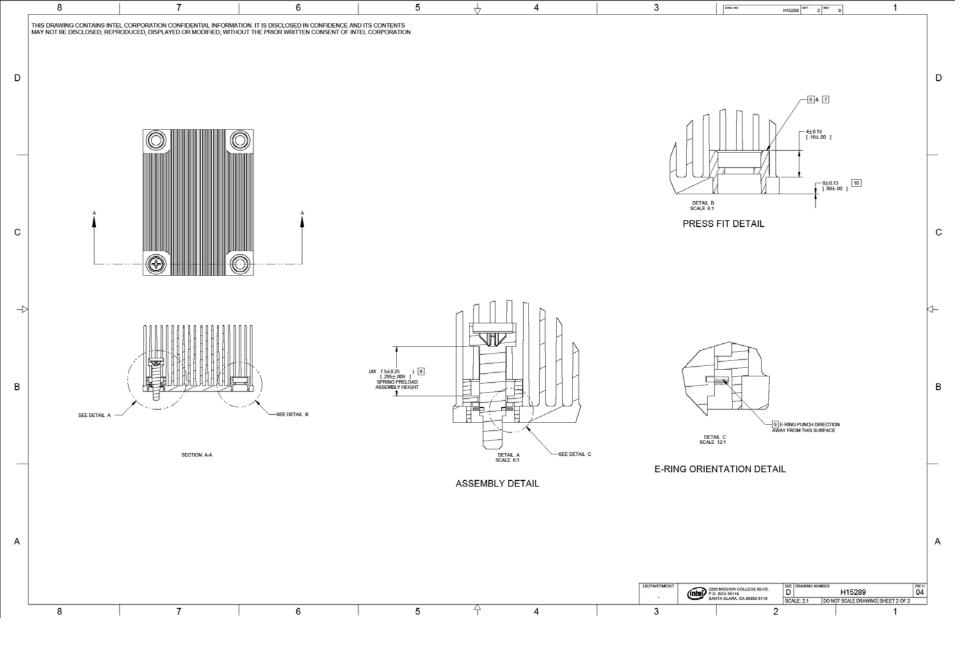

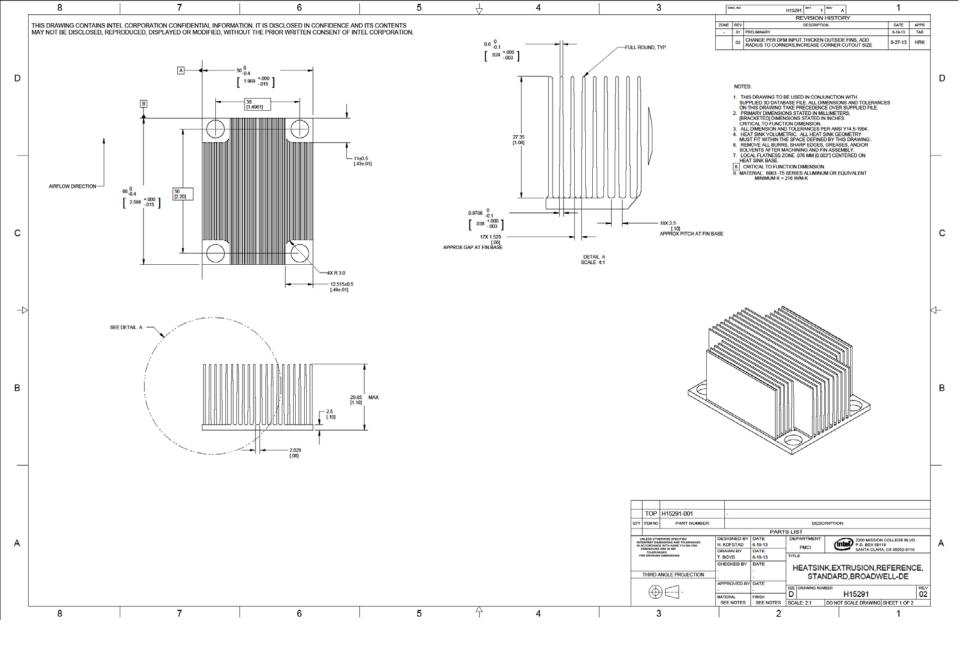

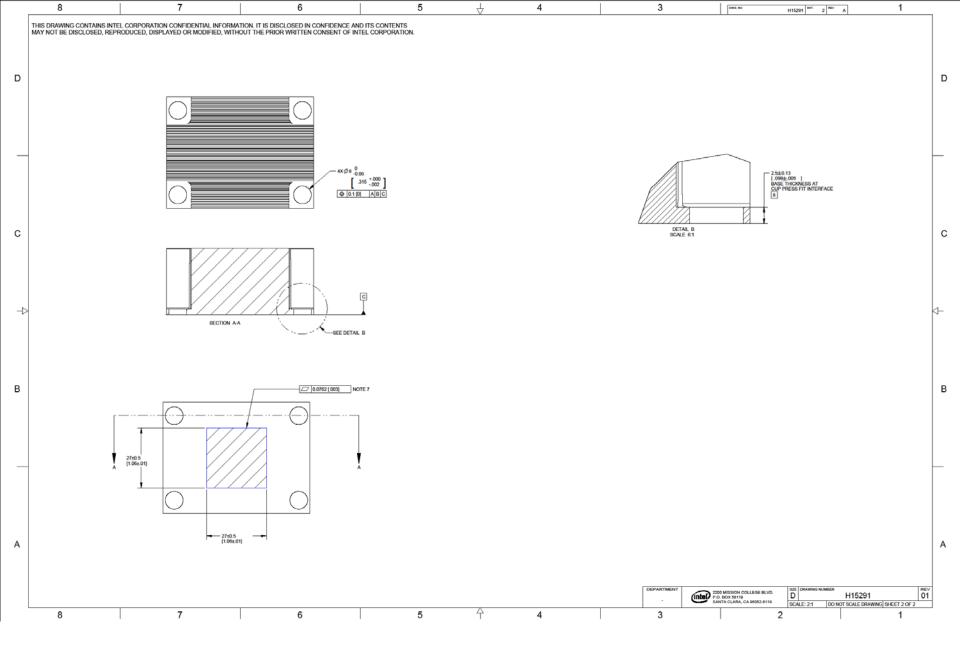

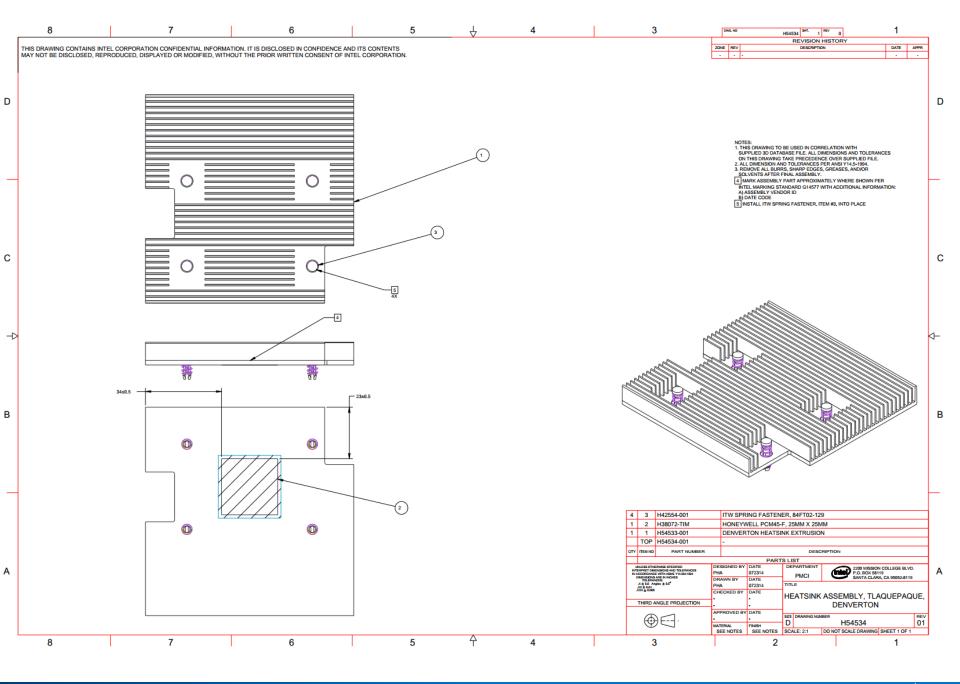

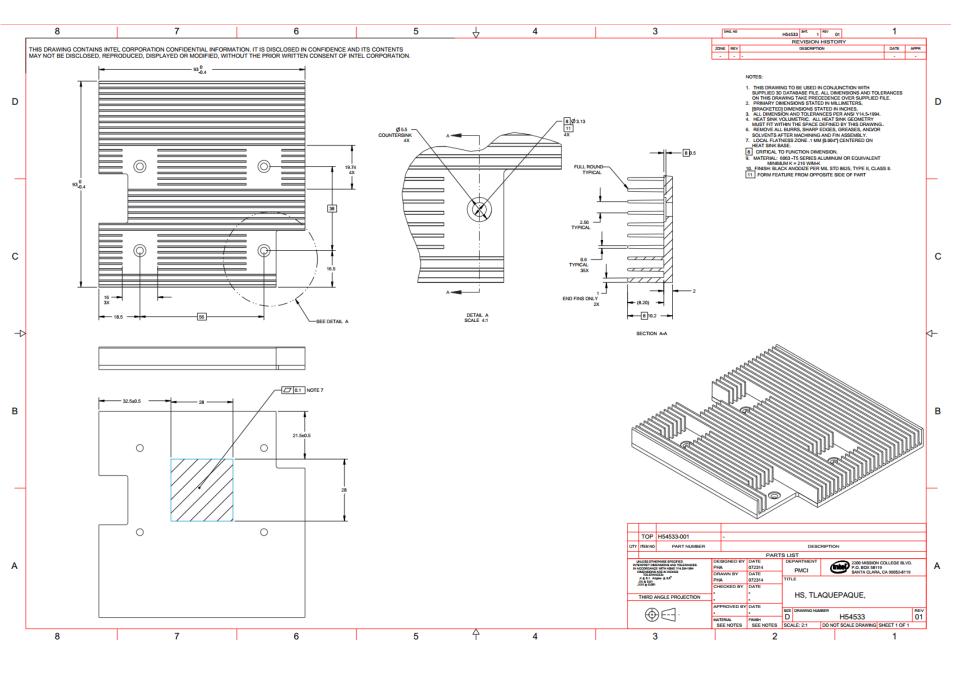

### Standard Height Heatsink Design - Microserver

#### Standard heatsink design details

- Material: Extruded aluminum heatsink

- Overall heatsink dimensions: 50mm(W) x 66mm(L) x 29.85 mm(H)

- Retention: four screws with backplate

- TIM: PCM45F

- Min required load is 27 lbf EOLife

- Fins: qty 20 (27.35mm tall)

- Pitch: 2.5mm

- Base thickness: 2.5mm

- Backplate is mainly used to provide higher TIM force

- Target power is >20W

See <u>Appendix B</u> for mechanical drawings and <u>Appendix H</u> for supplier info

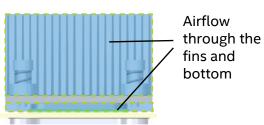

### Standard Heatsink Performance Curve

Heatsink performance ( $\Psi_{CA}$ , °C/W) as a function of airflow (CFM)

EoLife  $\Psi_{ca}$  +3\* $\sigma$  =  $\alpha$  +  $\beta$ \*(CFM)- $\gamma$

| α  | 0.303 |

|----|-------|

| β  | 1.600 |

| γ  | 0.718 |

| 3σ | 0.018 |

### ENTERPRISE STORAGE SEGMENT REFERENCE THERMAL SOLUTION

### Storage Form Factors

- Storage Bridge Bay

- Common canister definition for Storage enclosure.

- Refer to SBB Specification v.2.1 located at http://www.sbbwg.org/sbb\_specification/

- 1U Cloud Storage

- Low cost, 1U rack mount chassis using 3.5" hard drives.

### Storage Bridge Bay Overview

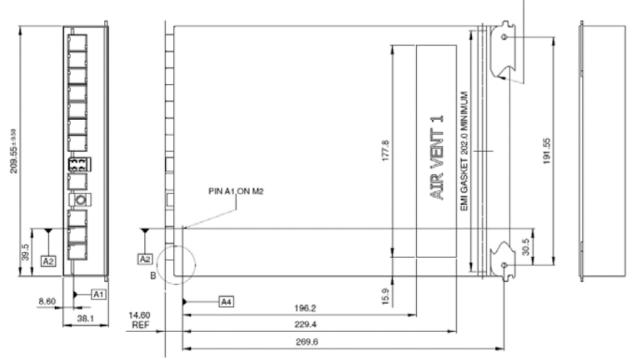

- Typically two SBB canisters plug into a midplane within chassis along with HDDs and PSUs.

- Overall maximum canister dimensions: 209.55 mm (W) x 284.5 mm (L) x 38.1 mm (H)

- Clearance above board for heatsinks: 27.5 mm (for 1 mm sheetmetal thickness)

- Airflow enters chassis at connector end and exits through one of two venting configurations.

For details, refer to the SBB Specification v.2.1 located at www.sbbwg.org

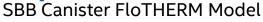

### SBB System Thermal Assumptions

- Chassis configuration: 2U with 24 2.5" HDDs

- Chassis external ambient: 35 °C

- Canister inlet ambient: 45 °C

- Canister airflow: 40 CFM

- Target exit temperature: 50 °C

- Vent 1 configuration due to excessive airflow bypass of the BDX-DE heatsink, Vent 2+3 configuration is not recommended for reference heatsink implementation.

- Trabuco Canyon Customer Reference Board layout.

2U Chassis w/ 24 HDDs (Front)

2U Chassis w/ 24 HDDs (Rear)

### System Reference Boundary Conditions

| SoC Power<br>Range SKU | Reference<br>heatsink<br>Concept | Local ambient<br>Temperature, T <sub>la</sub><br>(°C) | Airflow<br>through<br>heatsink<br>(CFM) | Notes |

|------------------------|----------------------------------|-------------------------------------------------------|-----------------------------------------|-------|

| 35W                    | SBB- Standard                    | 48                                                    | 3.9                                     | 1     |

| 25W                    | Low profile<br>(11 mm height)    | 48                                                    | 2.7                                     | 1     |

| 25W                    | Low profile++<br>(19 mm height)  | 48                                                    | 1.5                                     | 1     |

| 20W                    | Low profile                      | 48                                                    | 1.5                                     | 1     |

| Notes:                 |                                  |                                                       |                                         |       |

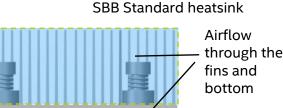

#### Low Profile heatsink

#### SBB Standard heatsink

<sup>1.</sup> These specifications are based on initial pre-silicon simulations, which will be updated as further characterization data becomes available.

### Heatsink application guidelines for Storage SKUs ≤25W

- The low profile heatsink can be used for Storage SKUs with TDP ≤20W in a SBB Canister.

- For the 25W SKU, the low profile heatsink requires increased airflow of 2.7 CFM through the heatsink. Alternatively, the heatsink height can be increased to 19 mm using same airflow rate (40 CFM canister flow).

Low Profile Heatsink

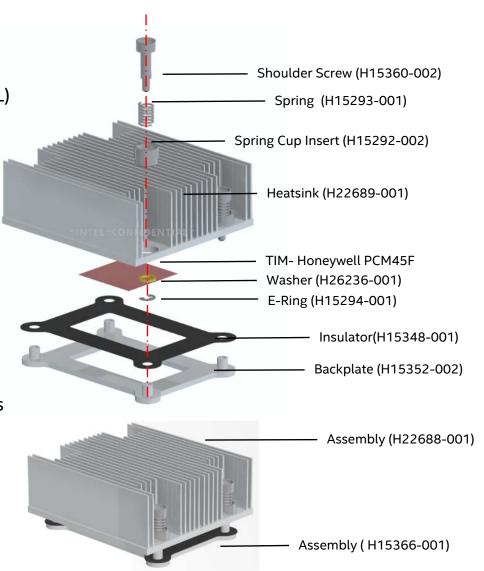

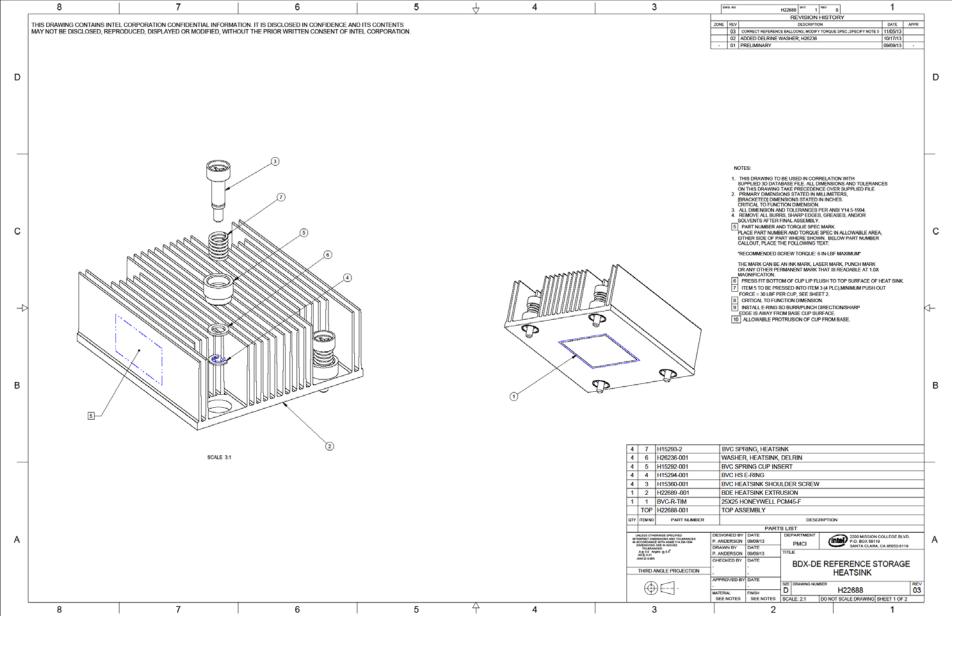

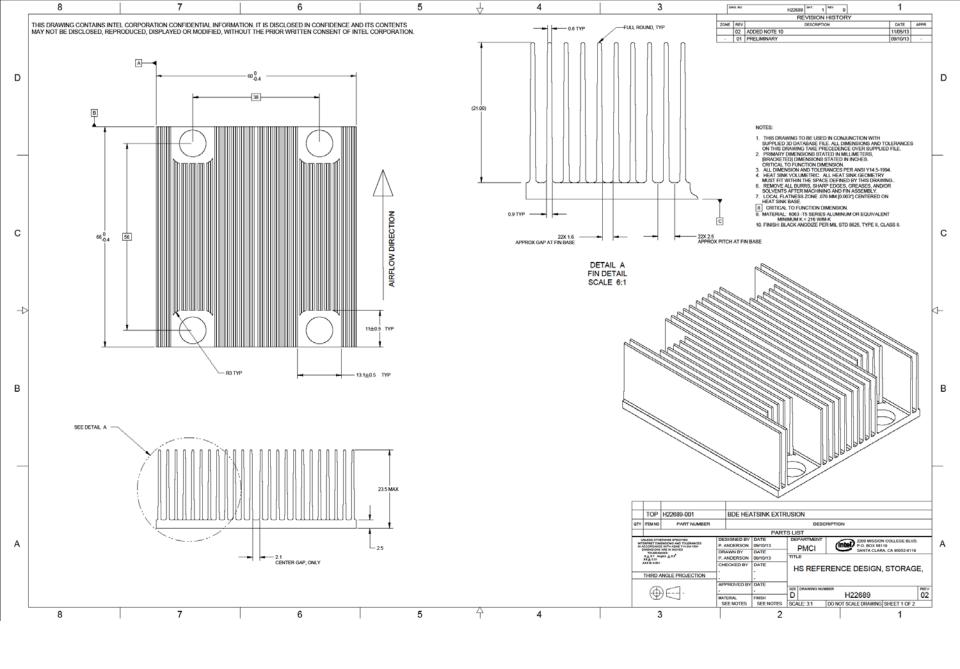

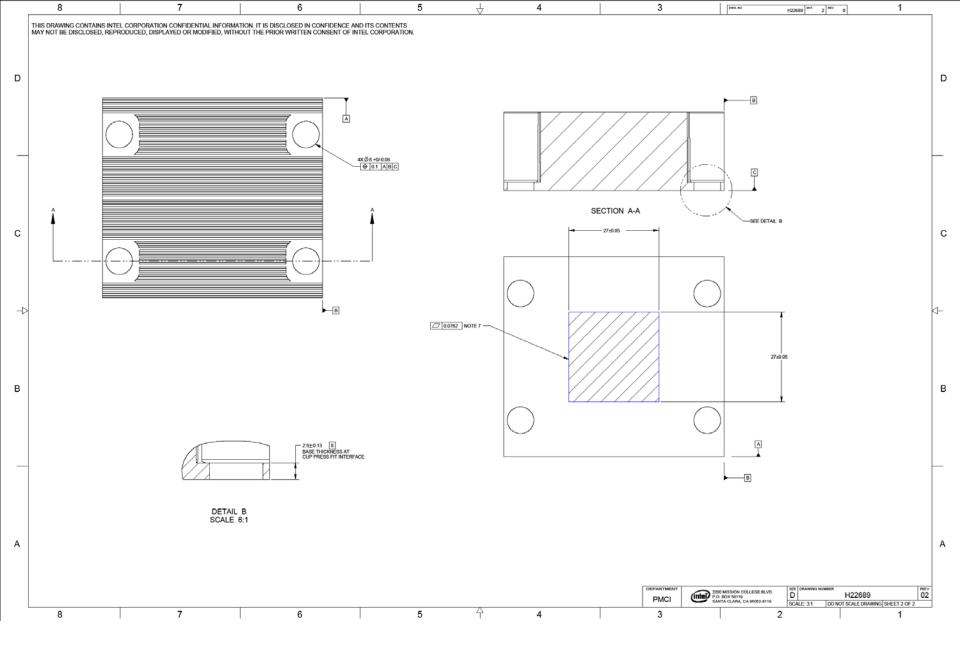

SBB Standard Heatsink Mechanical Design - Storage

#### SBB Standard heatsink

- Material: Extruded aluminum heatsink

- Overall heatsink dimensions: 60mm (W) x 66mm (L) x 23.5mm (H)

- Retention: four screws with backplate

- TIM: PCM45F

- Min required load is 27 lbf\* EOLife

- #Fins: 24 (21mm tall)

- Pitch: 2.5 mm

- Base thickness: 2.5 mm

- Backplate is mainly used to provide higher TIM force

- Target power is >25W

See <u>Appendix D</u> for mechanical drawings, some parts can be found in <u>Appendix B</u>.

See Appendix H for supplier info.

\*Note: design consideration for adequate thermal performance

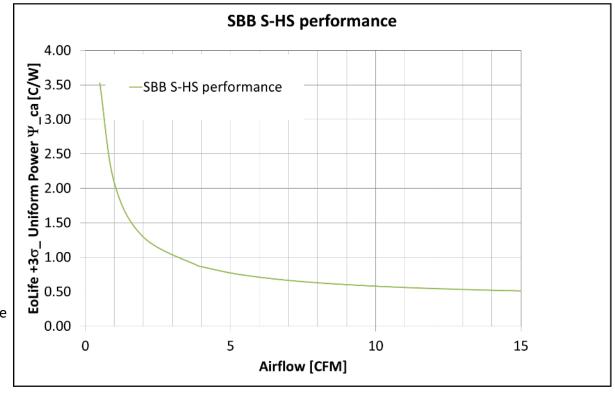

### SBB Standard Heatsink Performance Curve

Performance ( $\Psi_{ca}$ , °C/W) as a function of airflow (CFM)

EoLife  $\Psi_{ca}$  +3\* $\sigma$  =  $\alpha$  +  $\beta$ \*(CFM)\* $\gamma$

| α  | 0.392 |

|----|-------|

| β  | 1.732 |

| γ  | 0.876 |

| 3σ | 0.042 |

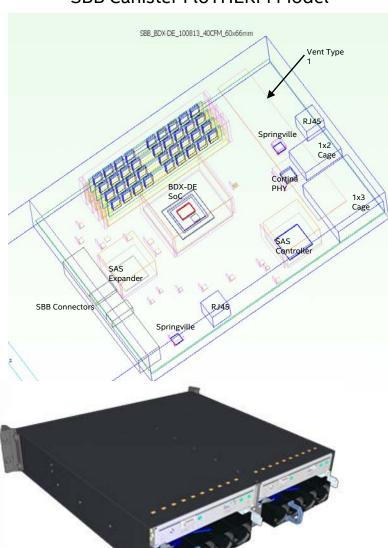

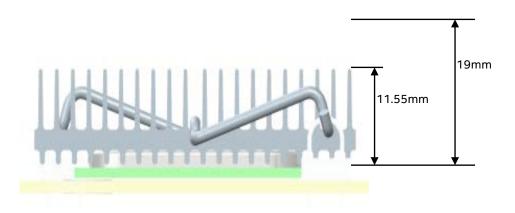

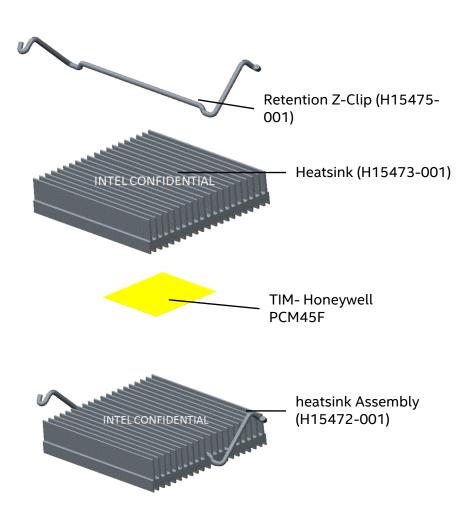

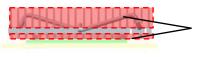

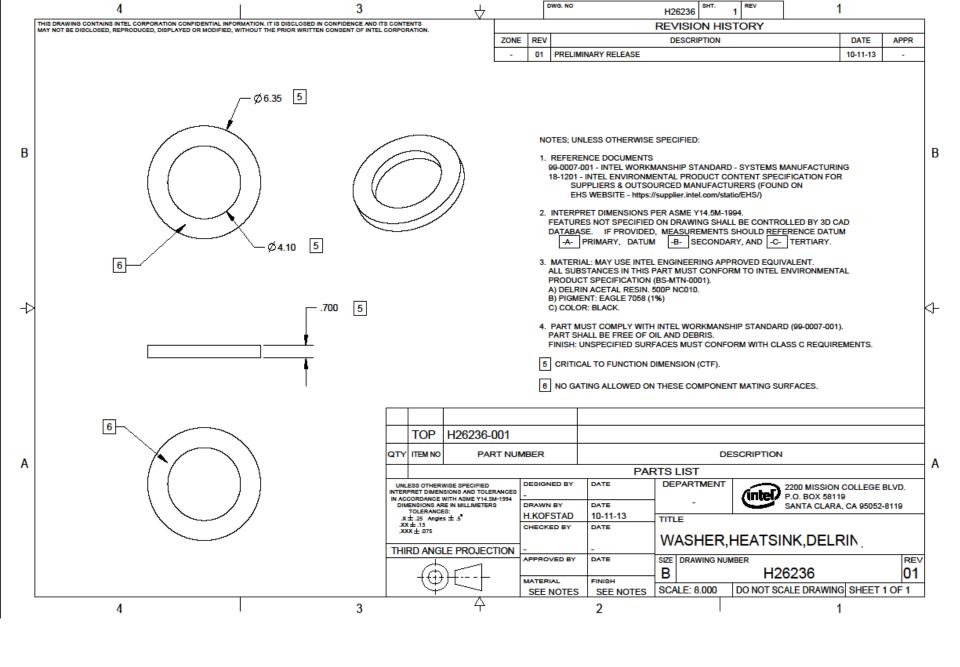

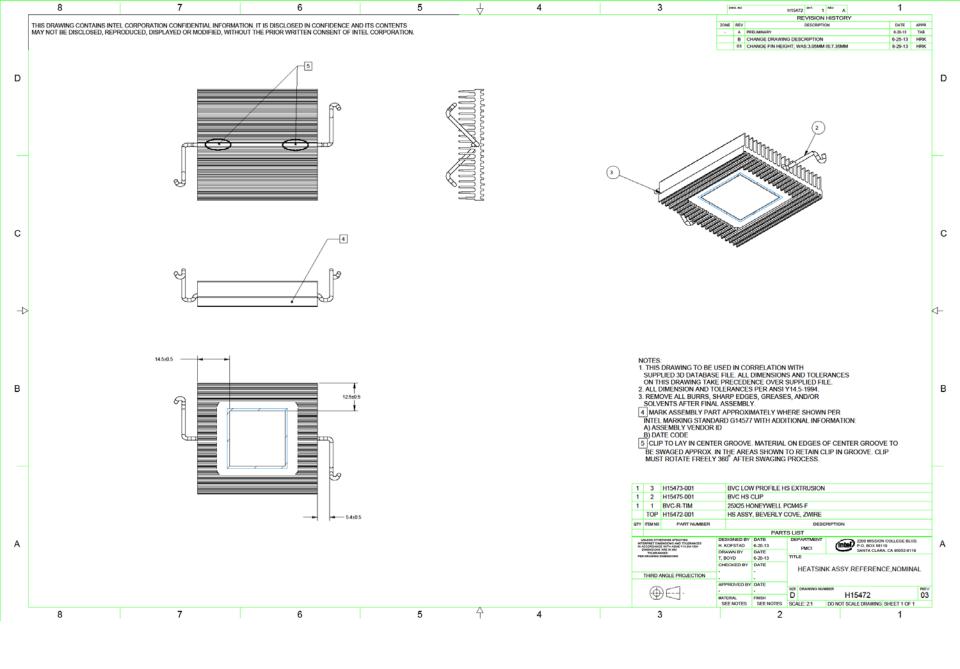

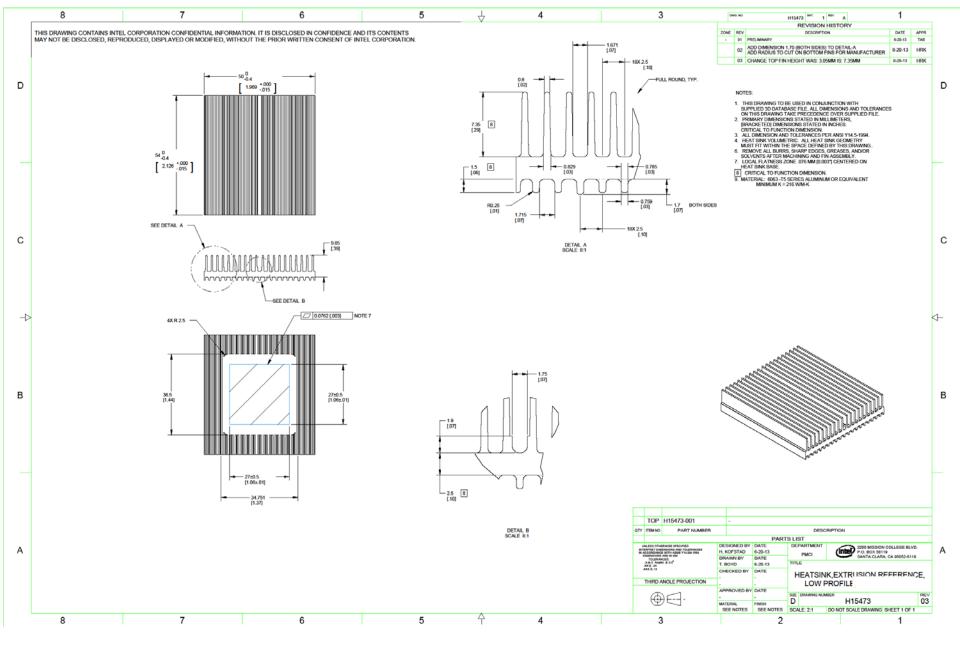

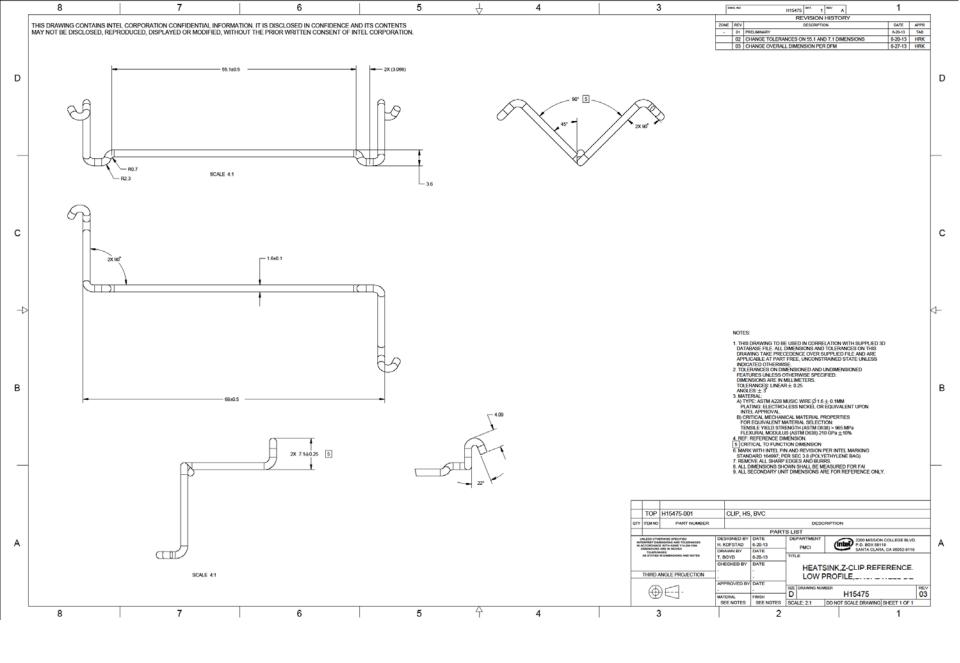

### Low Profile Heatsink Mechanical Design - Storage

#### Low profile Storage heatsink

- Material: Extruded aluminum heatsink

- Overall heatsink dimensions: 50mm(W)x54mm(L)x11.35mm(H)

- Retention: Z-clip/baseboard anchors

- TIM: PCM45F

- Min required load is 18Lbf\* EOLife

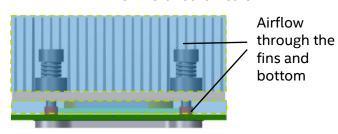

- #Fins: top 20 (7.35mm tall), bottom 21(1.5mm tall)

- Fin Pitch: 2.5mm( top and bottom)

- Base thickness: 2.5mm

- Target power is <=20W</li>

See <u>Appendix C</u> for mechanical drawings and <u>Appendix H</u> for supplier info.

\*Note: design consideration for adequate thermal performance

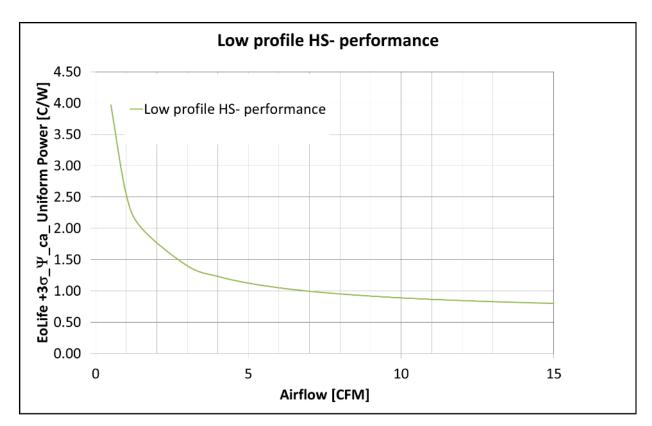

### Low Profile Heatsink Performance Curve

Performance (C/W) as a function of airflow (CFM)

EoLife

$$\Psi_{ca}$$

+3\* $\sigma$  =  $\alpha$  +  $\beta$ \*(CFM)\* $\gamma$

| α  | 0.563 |

|----|-------|

| β  | 1.981 |

| γ  | 0.782 |

| 3σ | 0.06  |

Low Profile Heatsink

Airflow through the fins on top and bottom

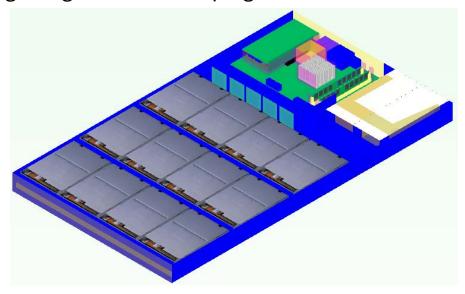

### 1U Cloud Storage Overview - Example

- Low cost, high density storage using standard 1U chassis.

- Typically 15 3.5" HDDs mounted in front of chassis, with fans located mid chassis between HDDs and motherboard.

- 40 mm fans positioned for fan fail cooling scenarios.

- Rotational vibration (RV) interference from array of HDDs needs to be mitgated. Some options include:

- Choice of HDD (Enterprise vs. Consumer, RV tolerant).

- HDD mounting using vibration damping materials.

## 1U Cloud Storage Reference Heatsink Design

- The following SoC heatsink boundary conditions are assumed for typical 1U rackmount Cloud Storage systems:

- Local ambient temperature = 50 °C

- Flow through heatsink (through fins and under heatsink) = 4.9 CFM

- No fan failure

- Thermal simulation results show that the Storage Bridge Bay reference heatsink is able to cool all Storage SKUs in a 1U Cloud Storage system.

- For a fan failure of a fan directly in front the heatsink, performance may be significantly impacted.

- Since the heatsink height was defined for the SBB form factor, additional thermal headroom can be obtained by by increasing fin height and reducing airflow bypass over the top of the heatsink.

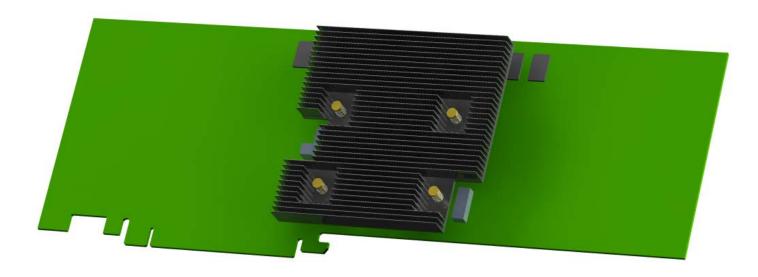

## PCIe\* Storage Host Bus Adapter Overview

- Storage Host Bus Adapter (HBA) plugs into enterprise storage server PCIe\* slot.

- Typically ¾ to full length PCIe form factor.

- PCI component height specification:

- Primary side max height = 14.47 mm

- Secondary side max component height = 2.35 mm

Intel® Xeon® Processor D-1500 Product Family SoC Reference Heatsink for PCIe HBA form factor

# PCIe\* Storage Host Bus Adapter Reference Heatsink Design

- The following SoC heatsink boundary conditions are assumed for worst case PCIe\* thermal environment:

- Local ambient temperature = 55 °C

- Airflow approach velocity = 150 LFM (linear ft/min)

- Reference heatsink design details:

- 93 mm x 93 mm x 10.2 mm

- Extruded aluminum

- Four (4) brass off-the-shelf spring loaded push pins (ITW\* 84FT02-129)

- Thermal simulation results show that the PCIe HBA reference heatsink is able to cool Storage SKUs with TDP below 20 W.

**Note**: The reference heatsink has not been validated and is presented as a concept only. Users should conduct their own thermal and mechanical validation testing prior to using in production.

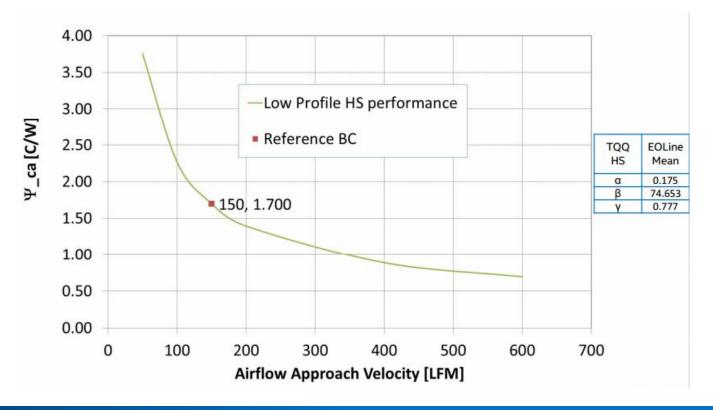

## PCIe\* Storage Host Bus Adapter Reference Heatsink Performance

- The following mean heatsink performance curve was derived:

- An adjustment of +0.13 °C/W is recommended to account for 3sigma variation and TIM degradation for End Of Life.

- The non-uniform heating correction factor provided <u>here</u> should be added as well.

## **COMMUNICATIONS SEGMENT REFERENCE THERMAL SOLUTION**

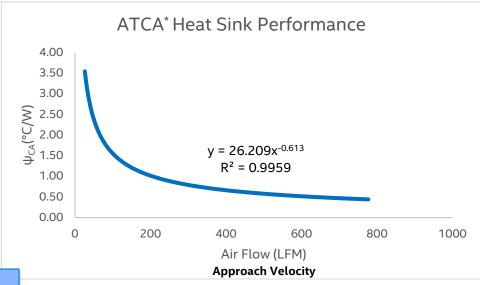

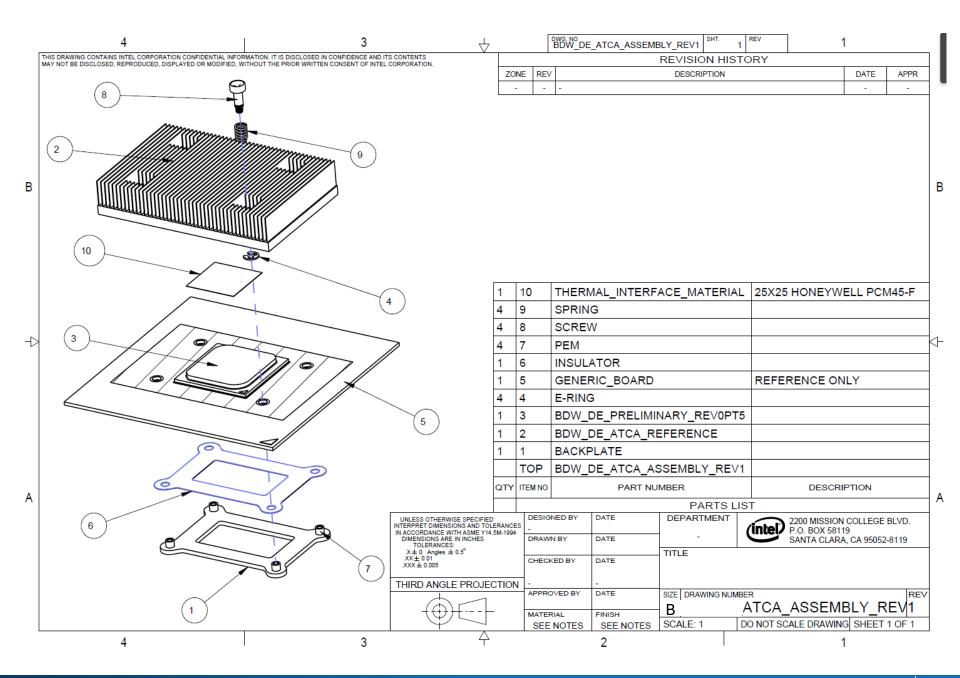

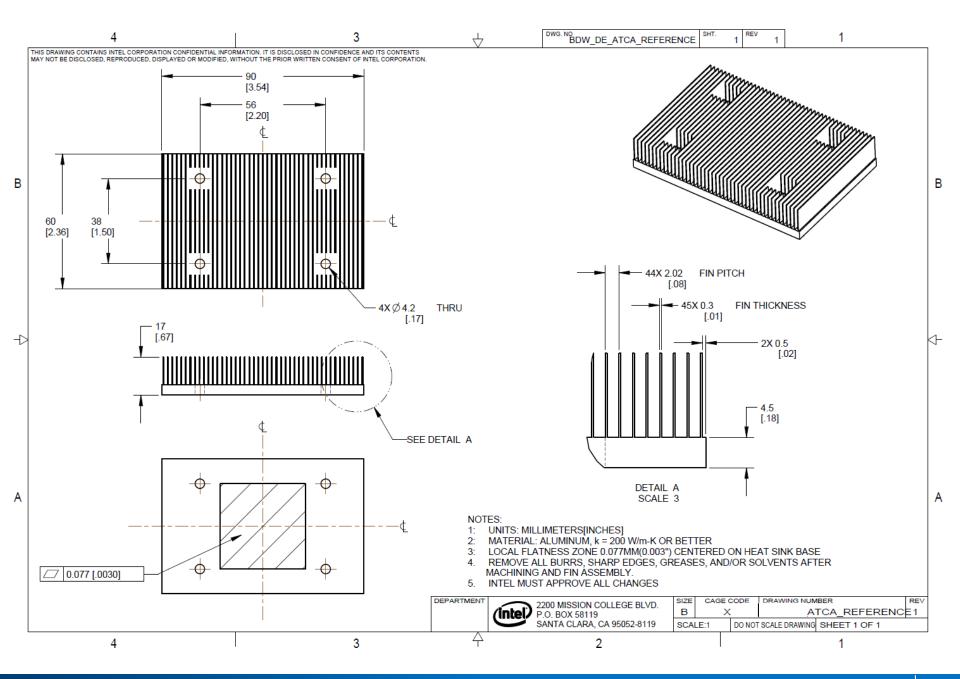

## ATCA\* Reference Heatsink Design

| Detailed ATCA* heatsink Properties |                                          |  |  |  |

|------------------------------------|------------------------------------------|--|--|--|

| Material                           | Aluminum (Al), k =200<br>W/m-K or better |  |  |  |

| Overall Dimensions (mm)            | 90 x 60 x 17                             |  |  |  |

| Base Thickness (mm)                | 4.5                                      |  |  |  |

| Fin Height (mm)                    | 12.5                                     |  |  |  |

| Fin Thickness (mm)                 | 0.3                                      |  |  |  |

| # of Fins                          | 45                                       |  |  |  |

- Performance data is based on test data.

- The non-uniform heating correction factor provided <a href="here">here</a> should be added as well.

- See Appendix D for detailed mechanical drawings.

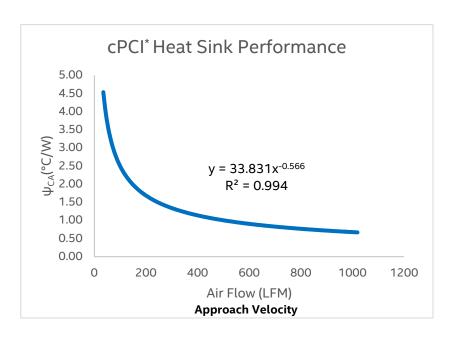

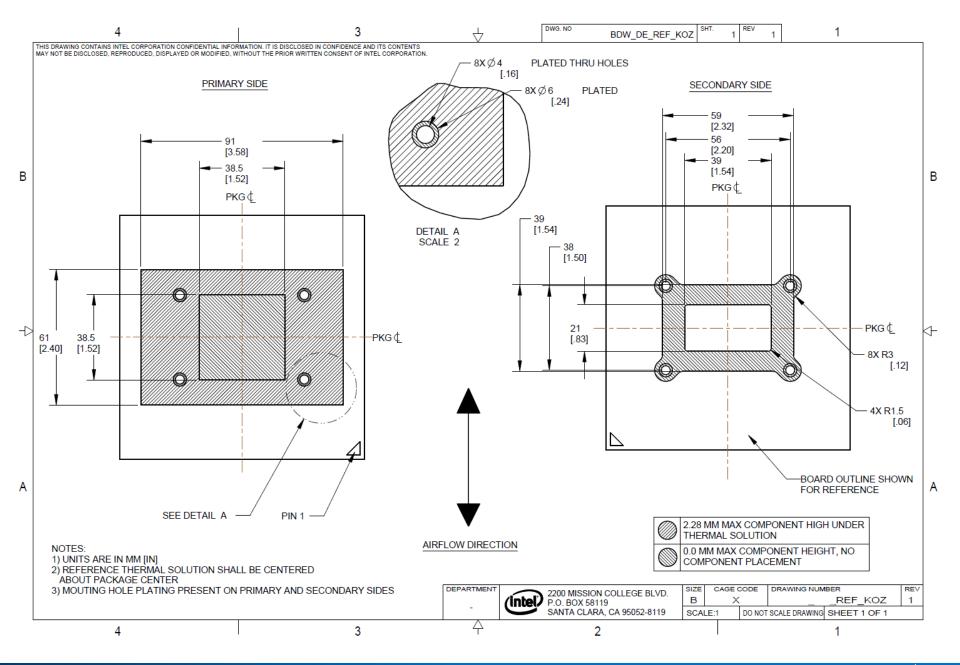

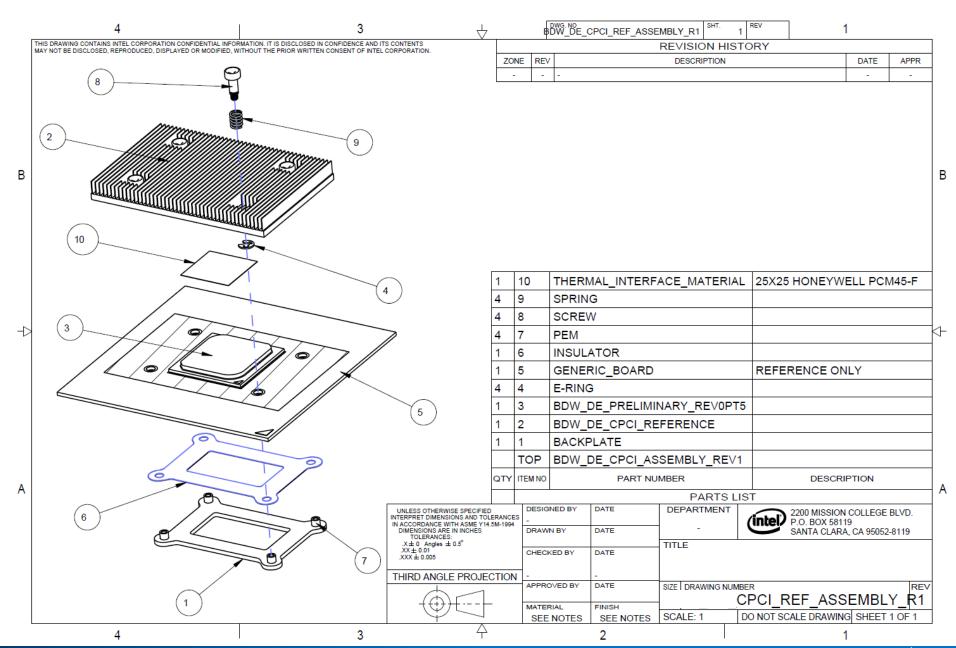

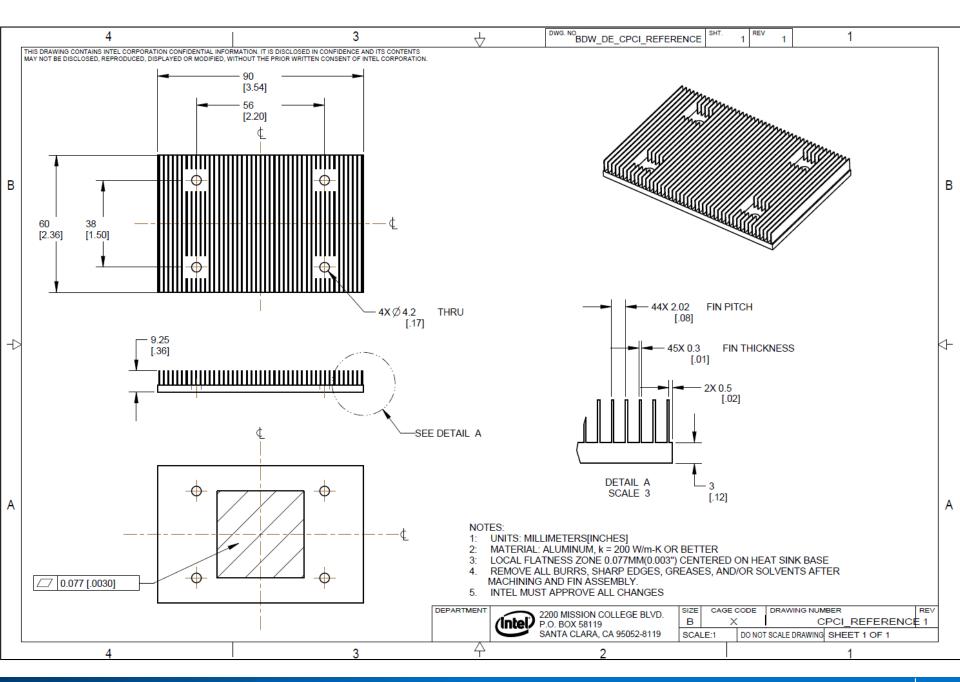

**CPCI\*** Reference Heatsink Design

| Detailed CPCI* Heatsink Properties |                                          |  |  |  |  |

|------------------------------------|------------------------------------------|--|--|--|--|

| Material                           | Aluminum (Al), k =200 W/m-K<br>or better |  |  |  |  |

| Overall Dimensions (mm)            | 90 x 60 x 9.25                           |  |  |  |  |

| Base Thickness (mm)                | 3.0                                      |  |  |  |  |

| Fin Height (mm)                    | 6.25                                     |  |  |  |  |

| Fin Thickness (mm)                 | 0.3                                      |  |  |  |  |

| # of Fins                          | 45                                       |  |  |  |  |

- Performance data is based on test data.

- The non-uniform heating correction factor provided <u>here</u> should be added as well

- See Appendix E for detailed mechanical drawings.

## APPENDIX A – INTEL® XEON® PROCESSOR D-1500 PRODUCT FAMILY PACKAGE MECHANICAL DRAWING

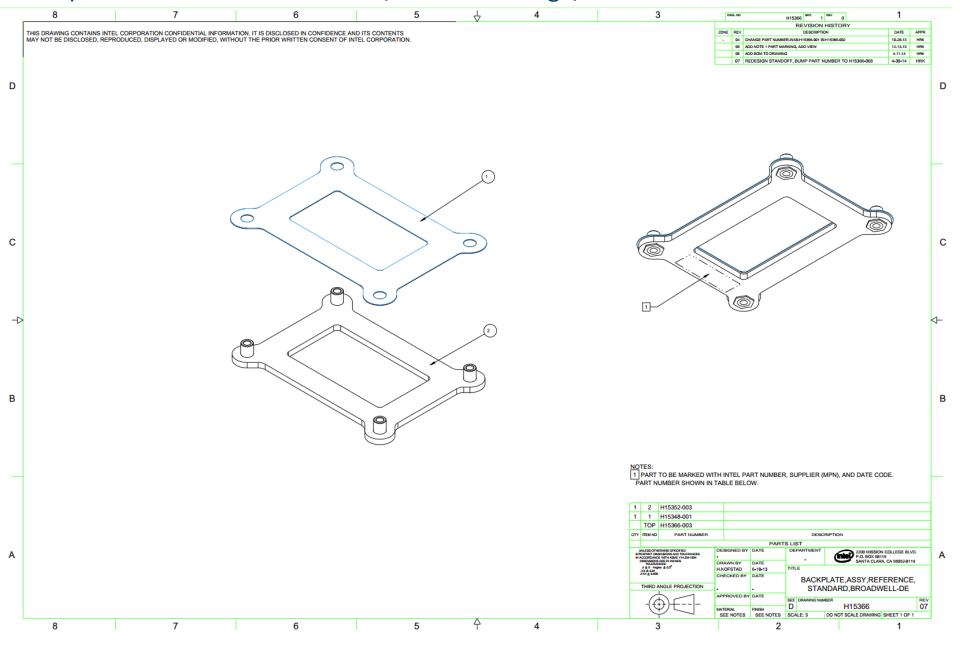

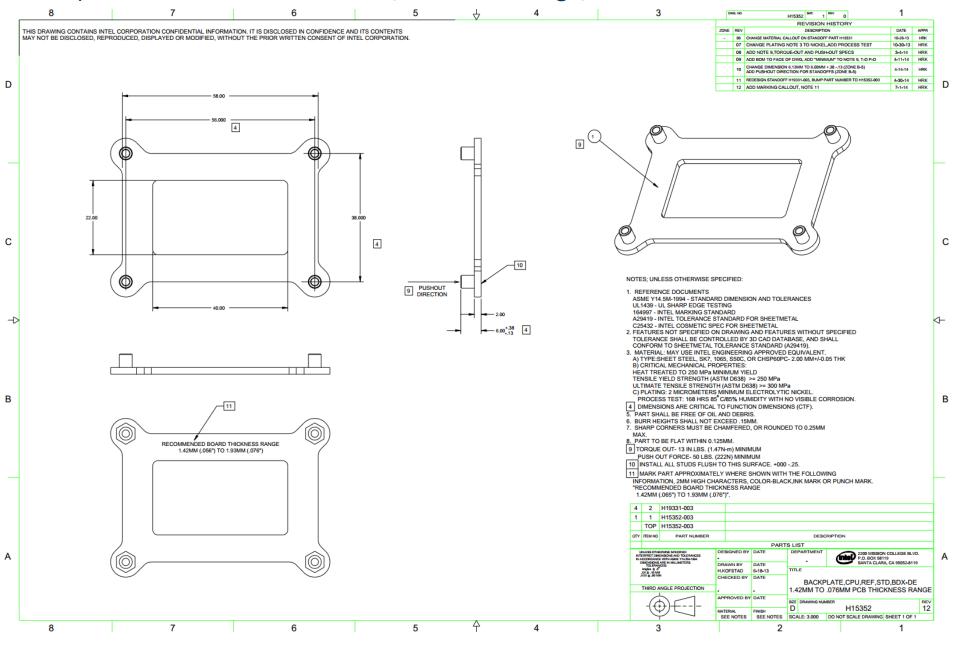

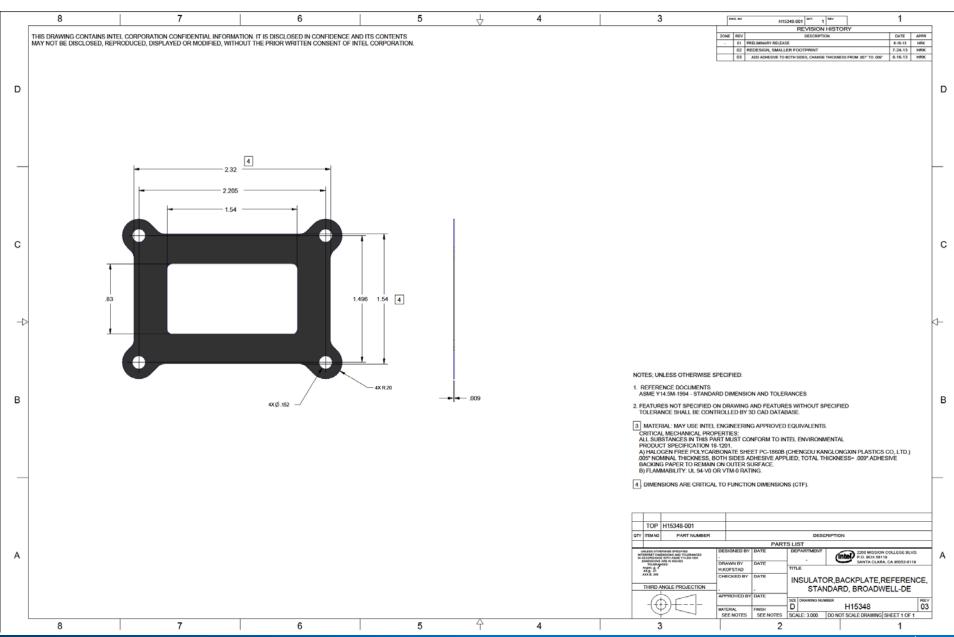

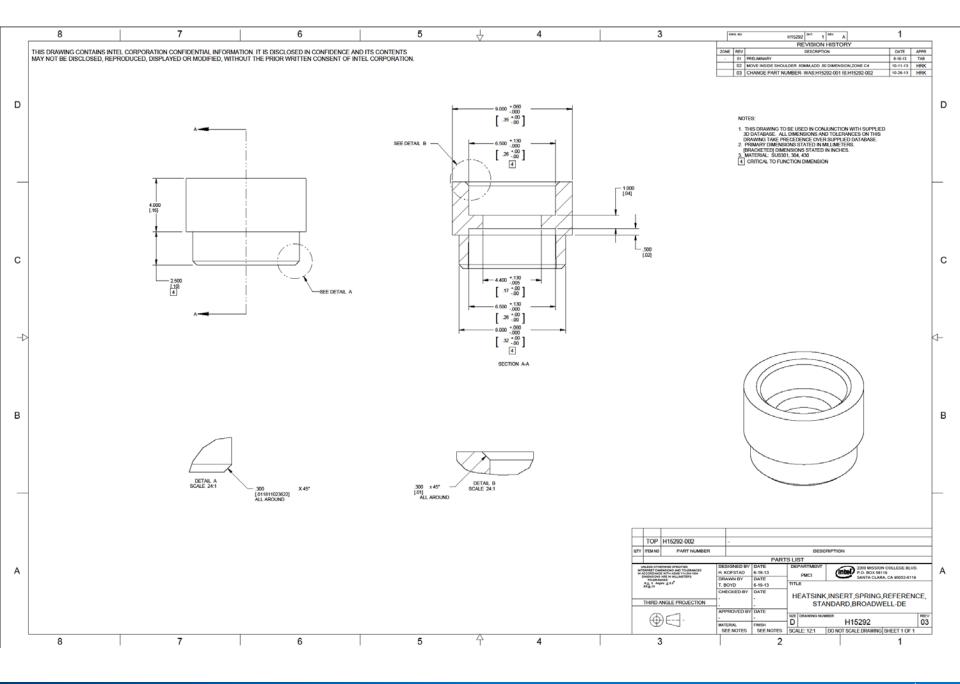

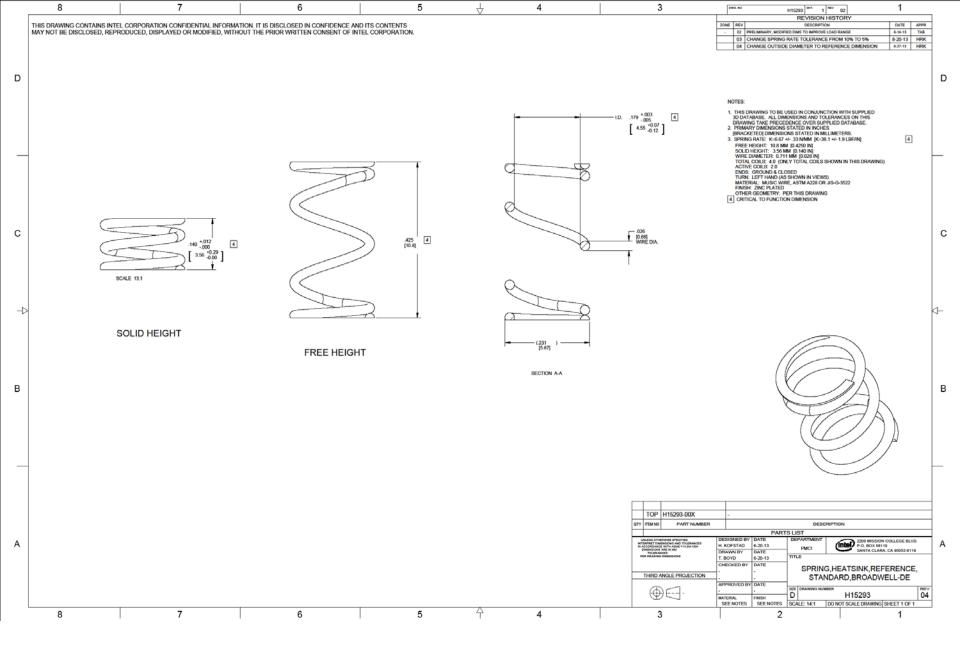

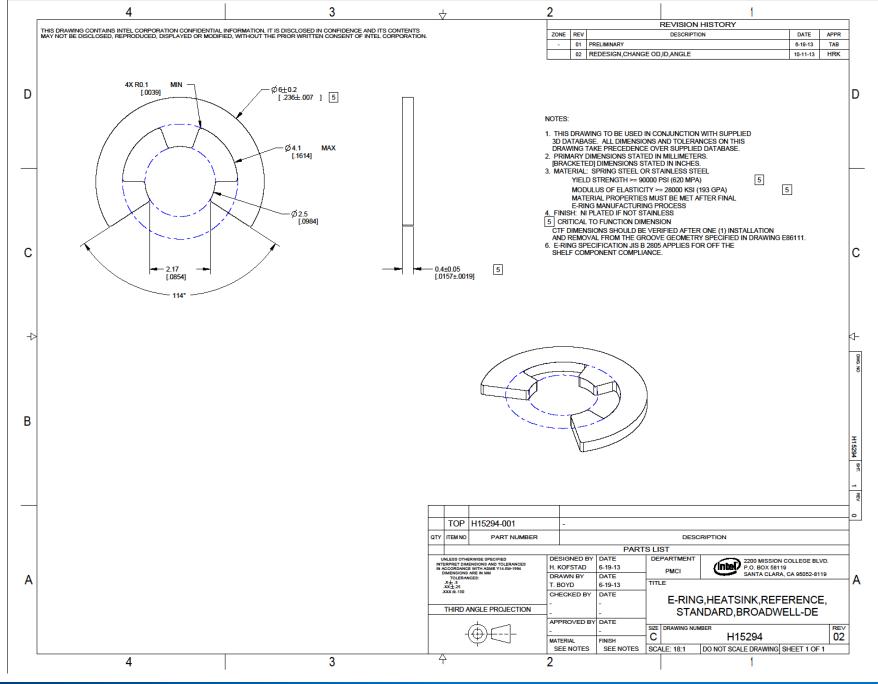

## APPENDIX B – STANDARD HEATSINK MECHANICAL DRAWINGS

### Backplate for 62 mil thick boards (56-76 mils range)

#### Backplate for 62 mil thick boards (56-76 mils range)

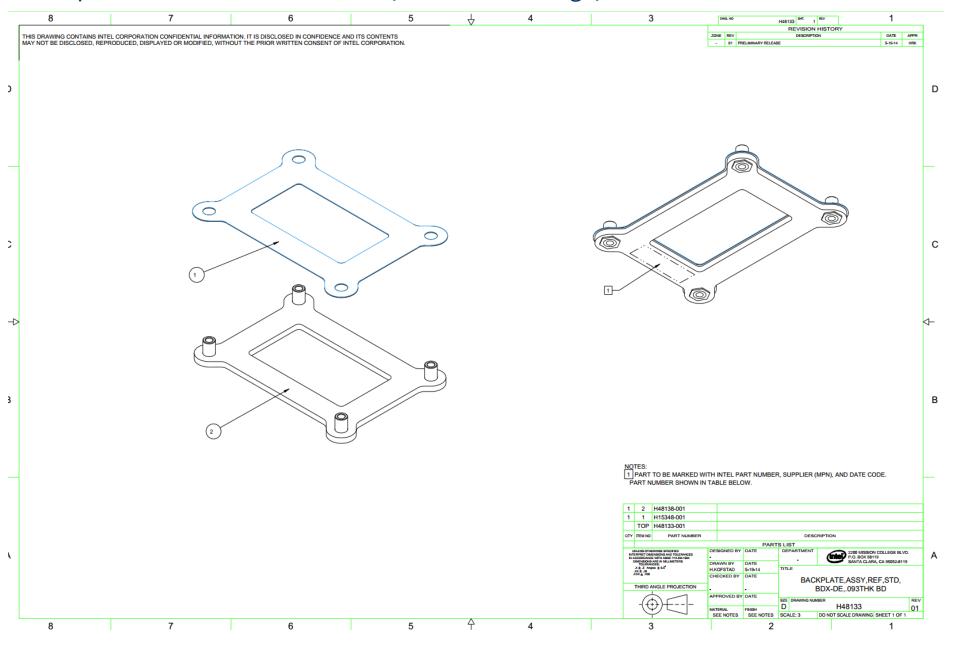

### Backplate for 93 mil thick boards (76-103 mils range)

Backplate for 93 mil thick boards (76-103 mils range) DEVISION HISTORY THIS DRAWING CONTAINS INTEL CORPORATION CONFIDENTIAL INFORMATION. IT IS DISCLOSED IN CONFIDENCE AND ITS CONTENTS DATE APPR ZONE REV DESCRIPTION MAY NOT BE DISCLOSED, REPRODUCED, DISPLAYED OR MODIFIED, WITHOUT THE PRIOR WRITTEN CONSENT OF INTEL CORPORATION. 5-19-14 HRK 01 PRELIMINARY RELEASE D D 4 4X R4.50 8X R3.000 4 С NOTES; UNLESS OTHERWISE SPECIFIED: PUSHOUT 1. REFERENCE DOCUMENTS ASME Y14.5M-1994 - STANDARD DIMENSION AND TOLERANCES UL1439 - UL SHARP EDGE TESTING 164997 - INTEL MARKING STANDARD A29419 - INTEL TOLERANCE STANDARD FOR SHEETMETAL C25432 - INTEL COSMETIC SPEC FOR SHEETMETAL 2. FEATURES NOT SPECIFIED ON DRAWING AND FEATURES WITHOUT SPECIFIED 4 6.79<sup>+.38</sup> TOLERANCE SHALL BE CONTROLLED BY 3D CAD DATABASE, AND SHALL CONFORM TO SHEETMETAL TOLERANCE STANDARD (A29419). 3. MATERIAL: MAY USE INTEL ENGINEERING APPROVED EQUIVALENT. A) TYPE:SHEET STEEL, SK7, 1065, S50C, OR CHSP60PC- 2.00 MM+/-0.05 THK B) CRITICAL MECHANICAL PROPERTIES HEAT TREATED TO 250 MPa MINIMUM YIELD TENSILE VIELD STRENGTH (ASTM D638) >= 250 MPa ULTIMATE TENSILE STRENGTH (ASTM D638) >= 300 MPa C) PLATING: 2 MICROMETERS MINIMUM ELECTROLYTIC NICKEL. В PROCESS TEST: 168 HRS 85° C/85% HUMIDITY WITH NO VISIBLE CORROSION. В 4 DIMENSIONS ARE CRITICAL TO FUNCTION DIMENSIONS (CTF). PART SHALL BE FREE OF OIL AND DEBRIS. 6. BURR HEIGHTS SHALL NOT EXCEED .15MM. 7. SHARP CORNERS MUST BE CHAMFERED, OR ROUNDED TO 0.25MM 8. PART TO BE FLAT WITHIN 0.125MM.

9 TORQUE OUT- 13 IN.LBS. (1.47N-m) MINIMUM PUSH OUT FORCE- 50 LBS. (222N) MINIMUM 10 INSTALL ALL STUDS FLUSH TO THIS SURFACE. +000 -.25. RECOMMENDED BOARD THICKNESS RANGE 1.93MM (.076") TO 2.62MM (.103") 11 MARK PART APPROXIMATELY WHERE SHOWN WITH THE FOLLOWING INFORMATION, 2MM HIGH CHARACTERS, COLOR-BLACK, INK MARK OR PUNCH MARK. "RECOMMENDED BOARD THICKNESS RANGE 1.93MM (.076") TO 2.62MM (.103")". 4 2 H48137-001 1 H15352-003 TOP H48138-001 QTY ITEM NO DESCRIPTION PARTS LIST 2200 MISSION COLLEGE BLVD. H.KOFSTAD 5-19-14 CHECKED BY DATE BACKPLATE, CPU, REF, STD, BDX-DE 1,93MM TO 2,62MM PCB THICKNESS RANGE H48138 SEE NOTES | SEE NOTES | SCALE: 3.000 | DO NOT SCALE DRAWING SHEET 1 OF 1 5

APPENDIX C - LOW PROFILE STORAGE HEATSINK MECHANICAL DRAWINGS

APPENDIX D - SBB STANDARD STORAGE HEATSINK MECHANICAL DRAWINGS

APPENDIX E – ATCA\* REFERENCE HEATSINK MECHANICAL DRAWINGS

APPENDIX F - CPCI\* REFERENCE HEATSINK MECHANICAL DRAWINGS

APPENDIX G – PCIE HBA REFERENCE HEATSINK MECHANICAL DRAWINGS

APPENDIX H - HEATSINK SUPPLIERS

## Heatsink Suppliers

| Component                                                                                                    | Intel Part<br>Number | Supplier PN | Supplier                                            | Supplier Contact Info                                                       | Notes     |

|--------------------------------------------------------------------------------------------------------------|----------------------|-------------|-----------------------------------------------------|-----------------------------------------------------------------------------|-----------|

| Intel® Xeon® Processor<br>D-1500 Product Family<br>Heatsink Assy (Spring<br>Screw Retention Type)            | H15289-002           | 00Z94630201 | Chaun-<br>Choung<br>Technology<br>Corp (CCI)        | Choung Contact: Monica Chih, Technology monica_chih@ccic.com.tw,            | 1,2,3,4,5 |

| Intel® Xeon® Processor<br>D-1500 Product Family<br>Backplate Assy                                            | H15366-002           | 00Z94600201 |                                                     |                                                                             |           |

| Intel® Xeon® Processor<br>D-1500 Product Family<br>Low Profile Heatsink (Z<br>Clip Type Retention)           | H15472-001           | 00Z94590101 |                                                     |                                                                             |           |

| Intel® Xeon® Processor<br>D-1500 Product Family<br>Heatsink Assy Storage<br>(Spring Screw<br>Retention Type) | H22688-001           | 00Z96050101 |                                                     |                                                                             |           |

| ATCA* Heatsink Assy                                                                                          | H69906-01            | TBD         | Chaun-<br>Choung<br>Technology<br>Corp (CCI)<br>TBD | Contact: Tina Huang,<br>tina_huang@ccic.com.tw, 886-<br>2-29952666 ext.1788 |           |

| CPCI* Heatsink Assy                                                                                          | H69905-01            | TBD         |                                                     |                                                                             |           |

#### Note

- 1. Supplier listing is provided by Intel as a convenience to its customers. Intel does not make any representations or warranties whatsoever regarding the quality, reliability, functionality, or compatibility of these devices.

- 2. All "Part Numbers" listed are in prototype phase and have not been verified to meet performance targets or quality and reliability requirements and are subject to change.

- 3. Supplier information provided in the table was deemed accurate when this document was released.

- 4. Customers planning on using the Intel reference design should contact the suppliers for the latest information on their product(s).

- 5. Customers must evaluate performance against their own product requirements.